10581

## A Digital Spectral Correlator for GMRT

A Thesis

Submitted for the Degree of

Master of Science (Kngg.)

in the Faculty of Engineering

Ву

V. M. Tatke

Centre for Electronics Design and Technology

INDIAN INSTITUTE OF SCIENCE

BANGALORE 560 012 (INDIA)

JANUARY 1998

## To my Parents

Who ran to help me when I fell, And would some pretty story tell, Or kiss the place to make it well? My Mother.

-Ann Taylor, 'My Mother'

Honour thy father and thy mother: that thy days may be long upon the land which the Lord thy God giveth thee.

> -Old Testament, Exodus, XX, 12 (5th. Commandment)

#### Abstract

#### A Digital Spectral Correlator for GMRT

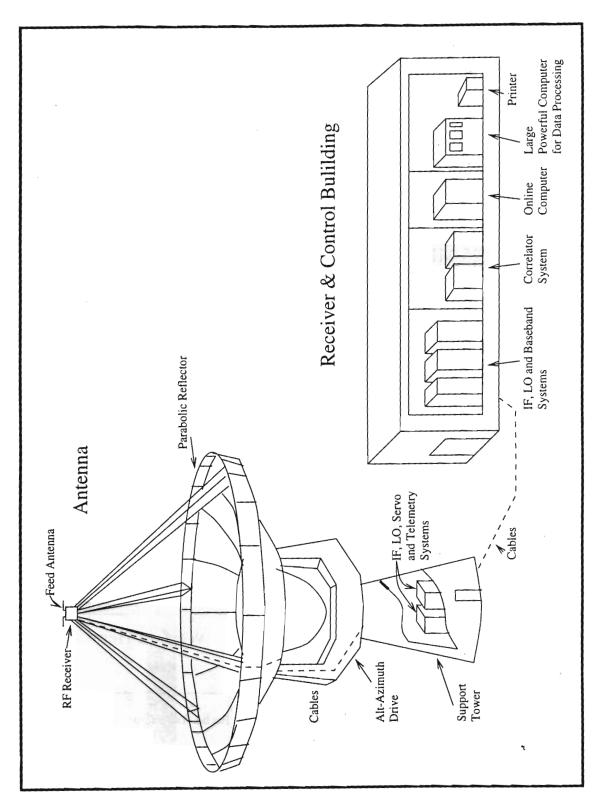

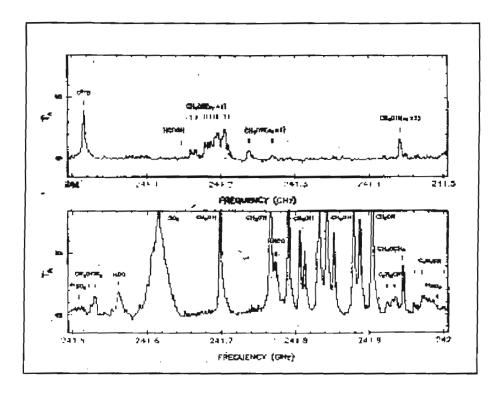

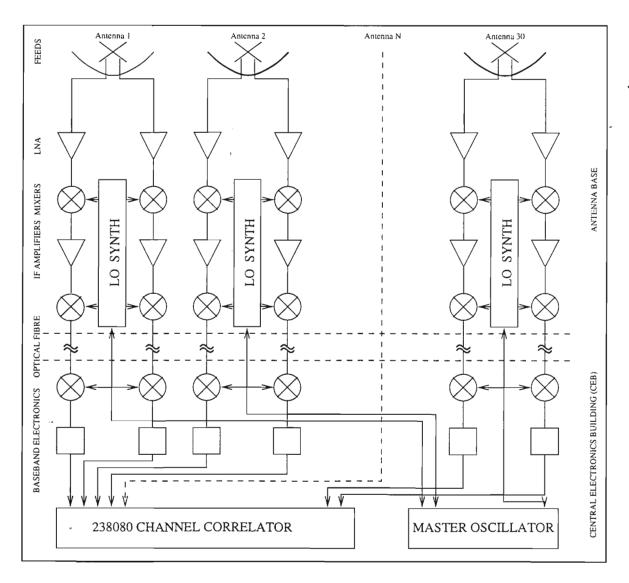

The Giant Metrewave Radio Telescope (GMRT), the world's largest radio telescope in the metrewave range, is an array of 30 antennas spread over approximately 25 Sq. Km. and situated about 80 Km. from Pune, India. It is being built as a major national facility for research in Astrophysics.

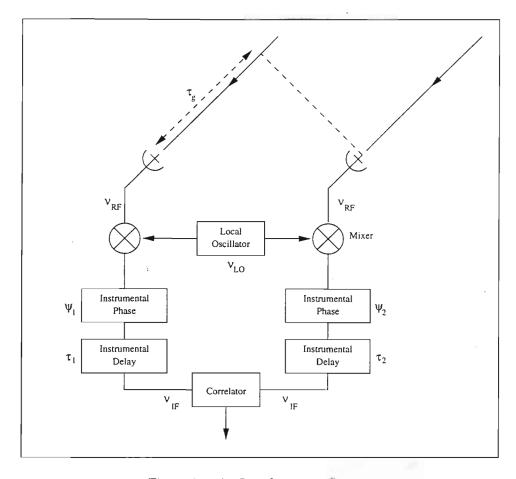

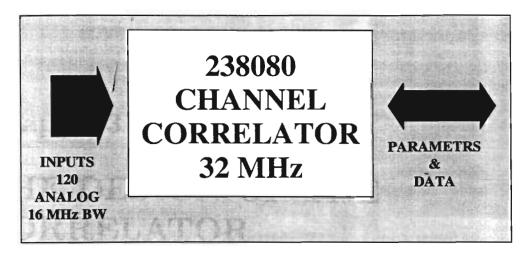

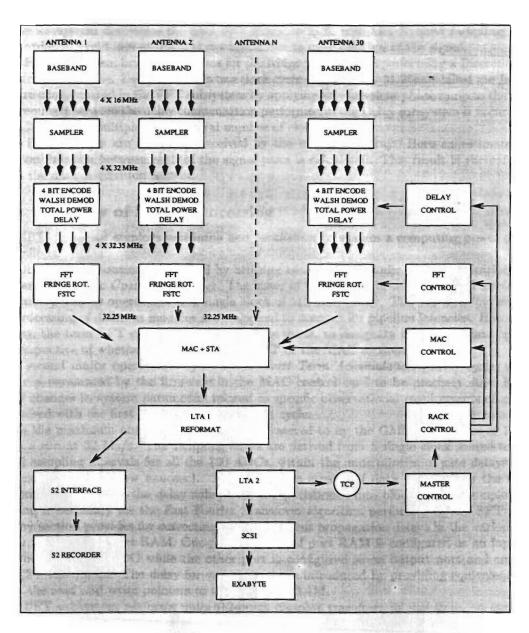

The GMRT antennas are equipped with highly sensitive superheterodyned radio receivers operating in six frequency bands between 50MHz and 1420 MHz, with a maximum bandwidth of 32MHz. The GMRT receiver electronics outputs four analog signals - two sidebands for each of the two polarizations - of 16MHz bandwidth for each of the 30 antennas. The 120 analog signal streams thus obtained are then input to the *Correlator* - the digital backend for real-time processing of these signals.

The GMRT correlator is required to compute the cross-power spectrum of signals from all  $435 \left(\frac{30X29}{2}\right)$  antenna pairs as well as their associated auto-power spectra. This required a computing power of about 400 Giga Flops, which necessitated the development of a special purpose hardware, specific to this application. The author was a core member of the team which designed and implemented this complex signal processing system. This thesis describes the basic specifications of the GMRT correlator and the design employed to meet them.

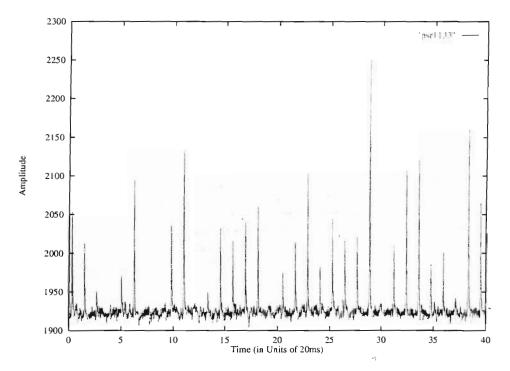

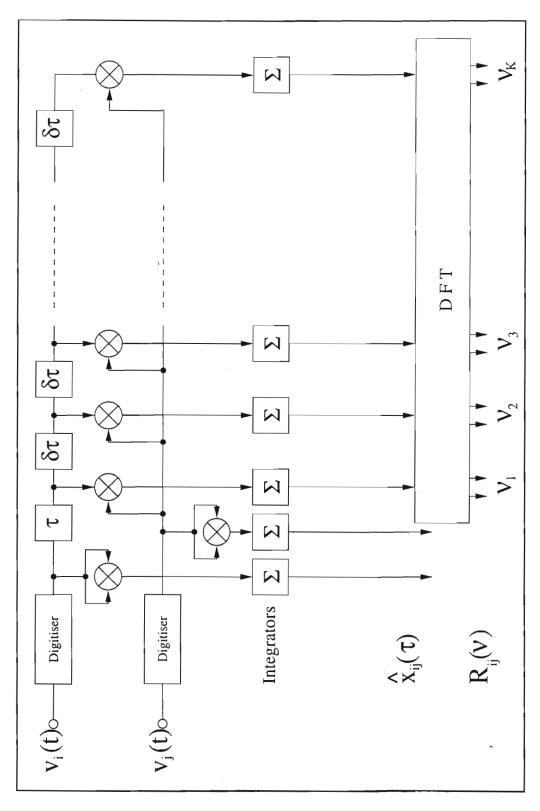

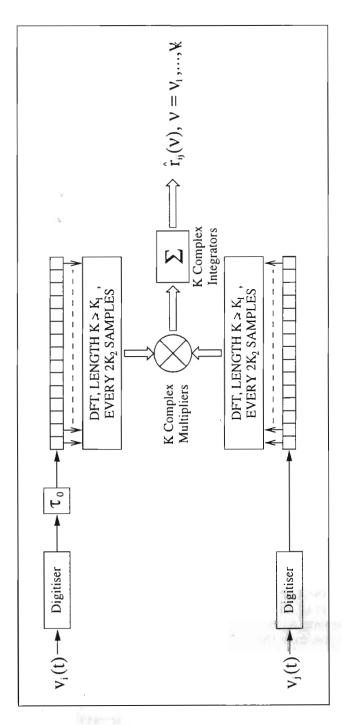

Each of the 120 analog signals is first sampled by the correlator and compensated for path length differences. A real-time Fourier transform is then performed on each of these to compute their spectra. The voltage spectra thus obtained are input to a multiplier array which computes the auto and cross-power spectra for all antenna pairs.

The correlator thus comprises of four major blocks, viz.,

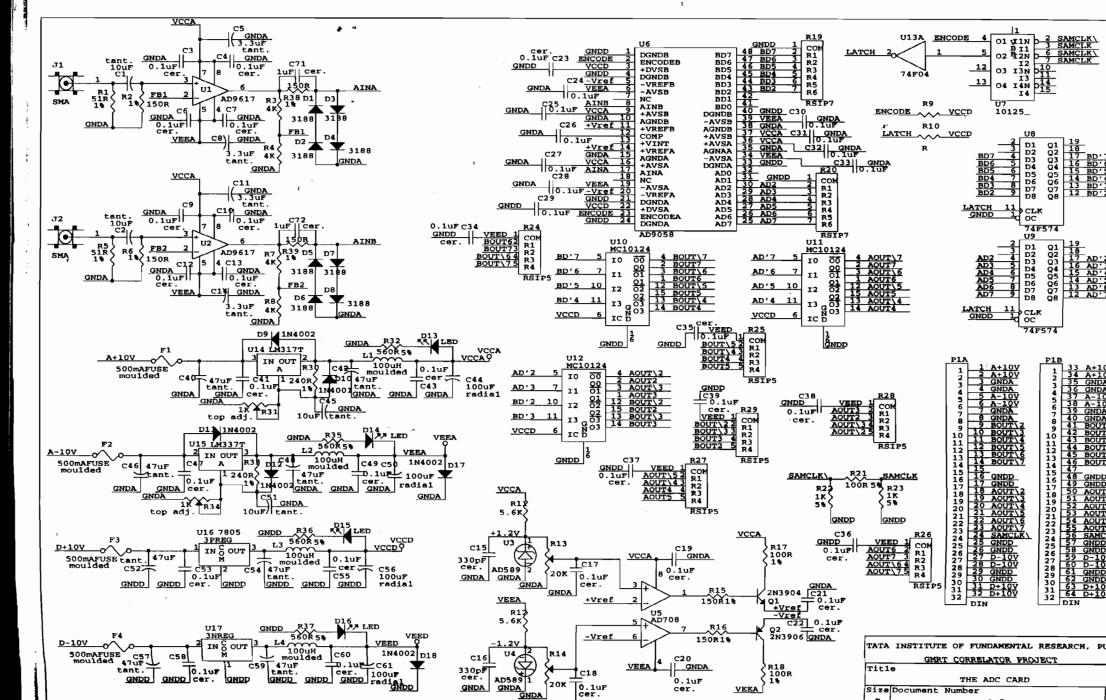

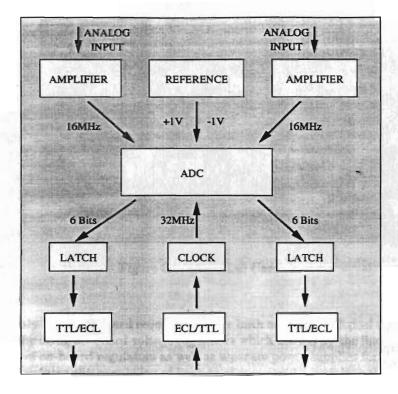

- 1. The ADC Subsystem: Samples the 120 analog inputs at 32MS/s.

- 2. The Delay Subsystem: Any value of delay upto 128  $\mu$ secs. can be compensated for, in steps of 32ns. These delay values are dynamically adjustable to compensate for effective path length differences produced due to rotation of the earth.

- 3. The FFT Subsystem: Performs upto 512-point Fourier transform in real-time to compute the spectra of each of the 120 inputs. It thus provides a maximum of 256 spectral channels for each input.

- 4. The MAC Subsystem: Multiplies the FFT outputs to compute the self and cross-power spectra for all the antenna pairs. It provides a total of 238080 complex accumulator channels.

The discussion presented in the thesis includes the circuit-design and packaging aspects of the various subsystems and the procedures employed to test, validate and integrate them.

#### Acknowledgements

Designing and building the GMRT Correlator has been, on the whole, an enriching and satisfying experience. I joined the GMRT Correlator team in October 1991 after graduation. Since then, till today, I have had the good fortune to have savoured the bonhomie of the GMRT fraternity in general, and the Correlator team in particular.

First and foremost, I wish to express my heartfelt gratitude for the encouragement and support which Prof. C.R. Subrahmanya has provided me in these past six years. As the head of the correlator group, he maintained an informal, friendly and close relationship with all members of the correlator group, including myself. I also have had the opportunity to exchange notes on topics reaching beyond those imposed by the correlator. I have always found in him a friend, philosopher and guide. I am extremely thankful to him for helping me a great deal with this thesis.

I would like to acknowledge and thank the support provided by Prof. H.S. Jamadagni all through the M.Sc. (Engg.) course. I wish to thank him for his several invaluable suggestions, which he rendered at various times during the course, helping me to see my work done at TIFR in a much broader perspective.

I regard Mr. Abhijit Datta as my mentor as far as the design of the correlator is concerned. I owe him the opportunity I had, to work on all the subsystems of the correlator. We, the members of the correlator group, owe him a well equipped laboratory and a cohesive team which laid the foundation for the present day correlator.

I would like to thank Dr. Yashwant Gupta, for his support and understanding, which has helped me to concentrate on the completion of this course. I am also thankful to him for going through the draft of this thesis and providing his valuable suggestions.

Among my colleauges, I have shared a very close relationship with Mr. Rakesh Malik. And, as a consequence, later I was fortunate to have shared a similar relationship with Mrs. Usha Malik. I owe Rakesh all the understanding of the GMRT and the correlator system, that I have at present. I also owe him a great deal as far as the MAC subsystem is concerned. I am thankful to him to have very cheerfully agreed to work on the MAC subsystem during my coursework at the IISc. And, to both, Usha and Rakesh, I owe a very cosy and homely atmosphere, in which I could completely be at ease.

Mr. Umesh Puranik and Mrs. Alka Bhatnagar, my other colleaugues in the correlator group made the endeavour a pleasure.

I wish to thank Mrs. Madhura Anturkar for having provided encouragement in my moments of sorrow. I am also thankful to her to have gone through my thesis and to have provided her valuable suggestions.

I am grateful to Mr. B. Rajendran and Mr. Ganesh Jangam, who with their skill have crafted our ideas into working systems. Their unflinching support and relentless toil has made it possible for us to see the light at the end of the tunnel.

I wish to thank Mr. Mahesh Burse, who after joining the Correlator group, very diligently took upon himself the task of debugging and integrating the final MAC subsystem, thereby leaving me free to concentrate completely on the completion of this thesis.

I would like to thank Mrs. Sunita Barve for all the help she extended in trying to collect the reference material needed for this thesis.

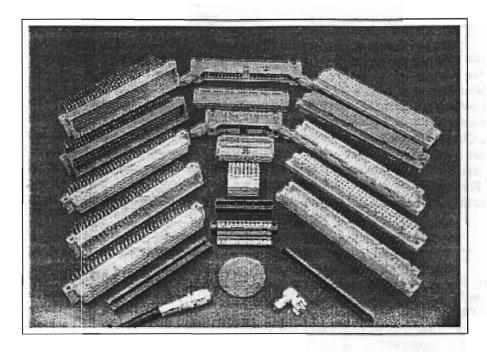

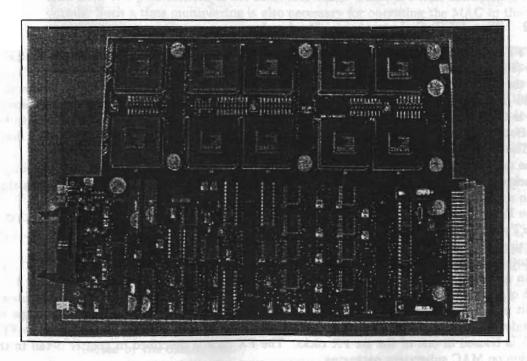

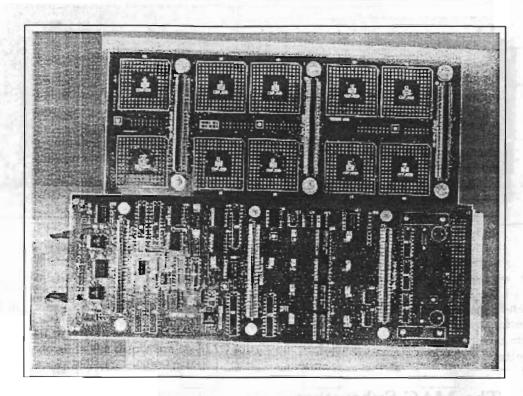

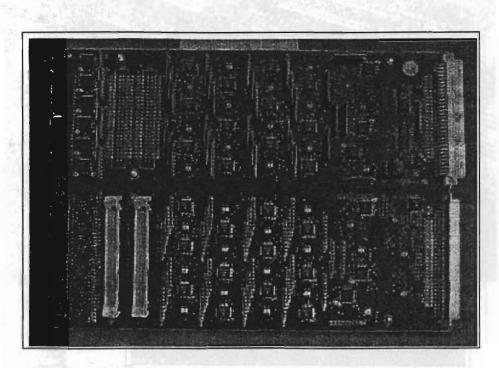

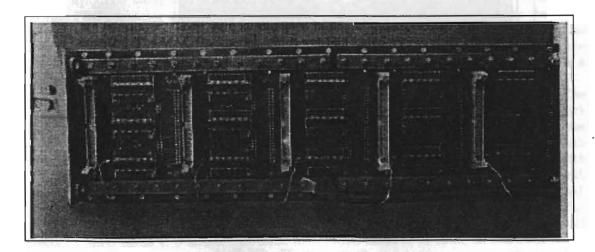

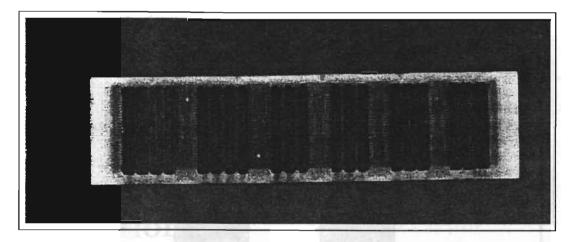

Among my other colleagues, I wish to thank Mr. Sanjay Bhatnagar, Mr. Divya Oberoi, Mr. Ajit Kulkarni and Mr. Nissim Kanekar to have made the stay in TIFR interesting. I would especially like to thank Mr. Divya Oberoi for having helped me with some of the photographs of the PCBs in this thesis.

In the end, my thoughts go out to my Parents and my Sisters, who have been my source of inspiration and have constantly encouraged me, all through. To them I owe a debt, too enormous to be expressed in words.

## Contents

| 1 | IN  | TRODUCTION                                        |

|---|-----|---------------------------------------------------|

|   | 1.1 | Correlation and Correlators                       |

|   | 1.2 | Radio Telescopes and Receivers                    |

|   |     | 1.2.1 The Radio Telescope                         |

|   |     | 1.2.2 How does the Radio Telescope SEE?           |

|   |     | 1.2.3 Kinds of Radiation                          |

|   |     | 1.2.4 Radio-Telescope Receivers                   |

|   |     | 1.2.5 Modern Synthesis Arrays                     |

|   | 1.3 | The Giant Metrewave Radio Telescope (GMRT)        |

| 2 | DE  | FINING THE PROBLEM 2                              |

|   | 2.1 | The Context of the Correlator                     |

|   |     | 2.1.1 Requirements due to Astronomical Objectives |

|   |     | 2.1.2 Requirements due to the Receiver System     |

|   |     | 2.1.3 Requirements due to the Array Configuration |

|   | 2.2 | The Type of Spectral Correlator                   |

|   |     | 2.2.1 The XF and FX Correlator                    |

|   | 2.3 | The GMRT Correlator - As a Black Box              |

| 3 | TH  | E DESIGN OF THE CORRELATOR 36                     |

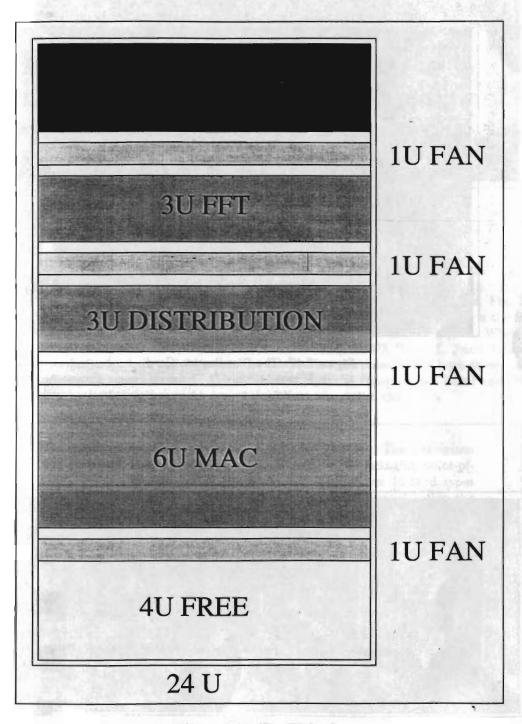

|   | 3.1 | A Bird's Eye-View of the Correlator               |

|   |     | 3.1.1 The Flow of Data                            |

|   |     | 3.1.2 Overview of Signal Processing               |

|   |     | 3.1.3 Packaging Considerations                    |

|   | 3.2 | The Specifications of the Subsystems              |

|   |     | 3.2.1 The ADC Subsystem                           |

|   |     | 3.2.2 The Delay Subsystem                         |

|   |     | 3.2.3 The FFT Subsystem                           |

|   |     | 3.2.4 The MAC Subsystem                           |

|   | 3.3 | The ADC Subsystem                                 |

|   |     | 3.3.1 The ADC Subsystem: Circuit Design           |

|   |     | 3.3.2 The ADC Subsystem: Packaging                |

|   | 3.4 | The Delay Subsystem                               |

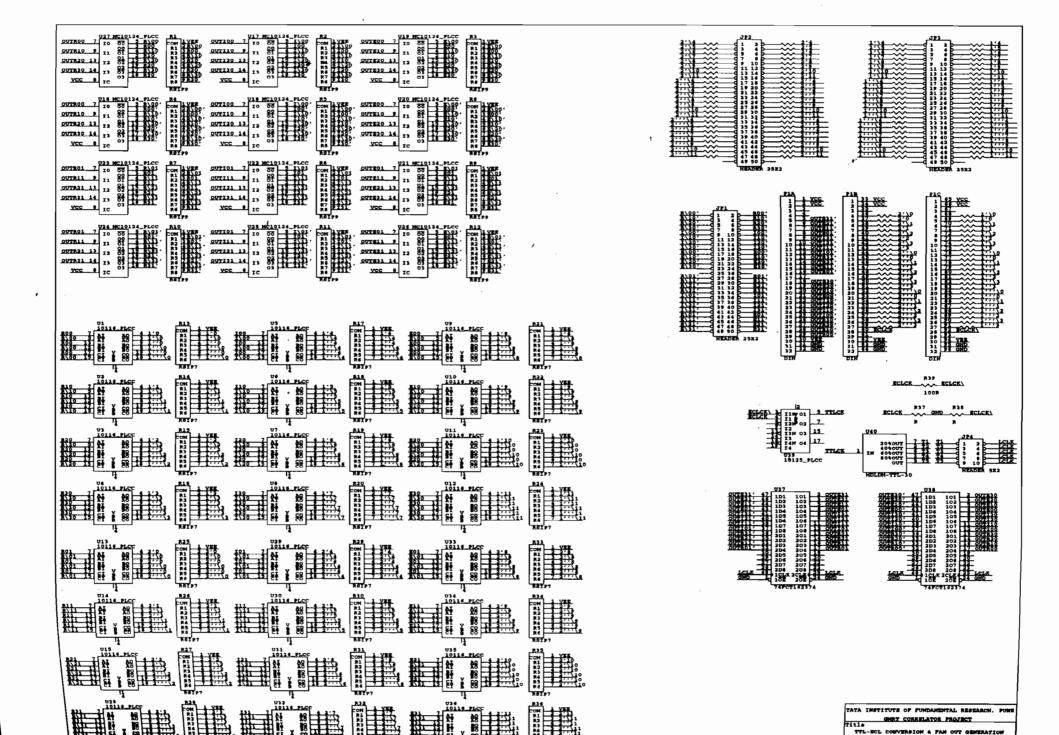

|   |     | 3.4.1 The Delay Subsystem: Circuit Design         |

|   |     | 3.4.2 The Delay Sub-system: Packaging             |

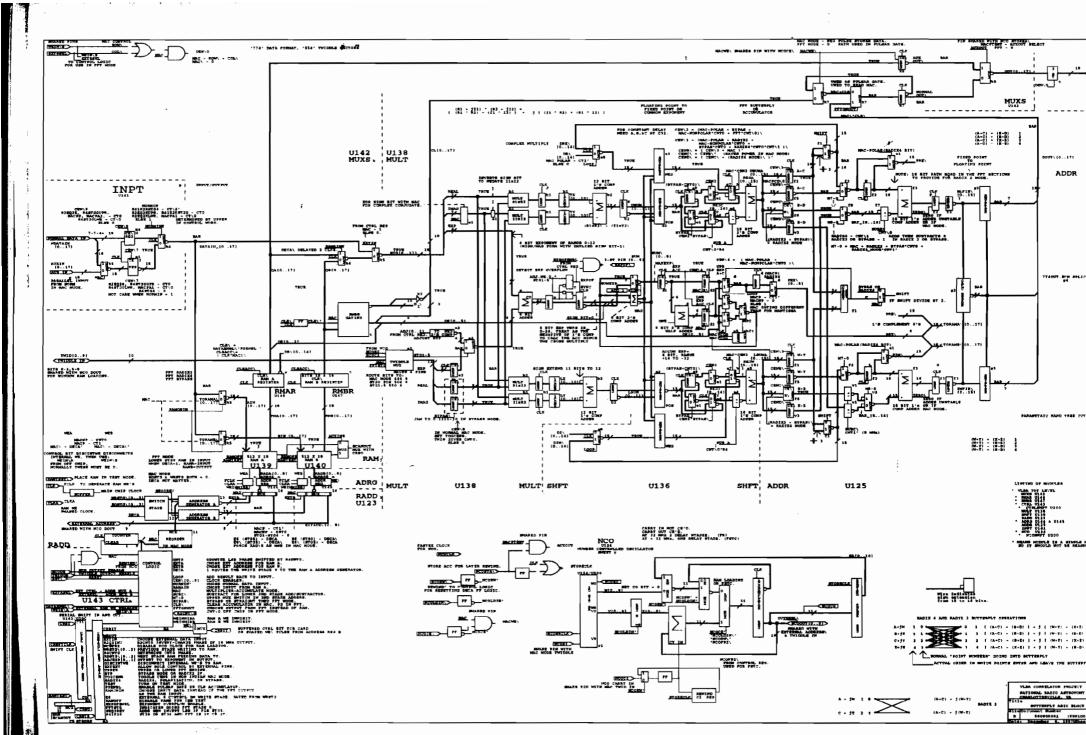

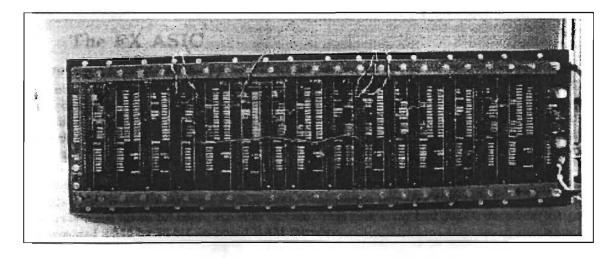

|   | 3.5 | The FX ASIC                                       |

|   |     | 3.5.1 Modes                                       |

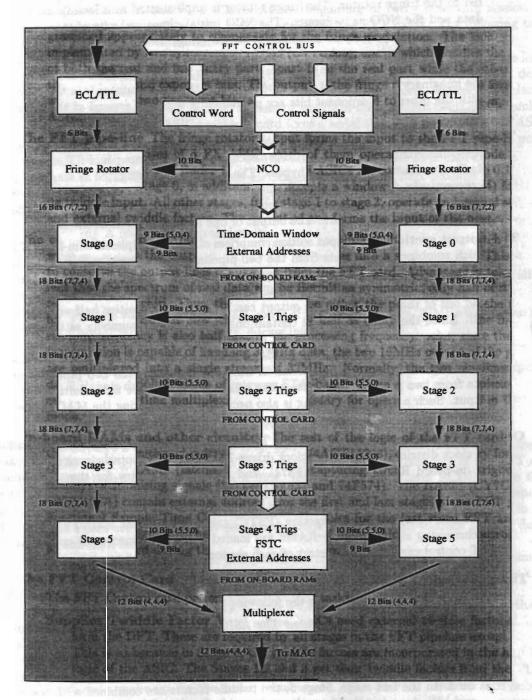

|   |     | 3.5.2 ASIC Block Diagram                          |

|   |     | 3.5.3 The Control Word                            |

|   |     | 2.5.4 Hardware Simple                             |

## Contents

| 1 | IN   | TRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • | 1.1  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   | 1.2  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   | 1.4  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   |      | The state of the s |

|   |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   |      | 1.2.4 Radio-Telescope Receivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   | 1 0  | 1.2.5 Modern Synthesis Arrays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   | 1.3  | The Giant Metrewave Radio Telescope (GMRT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2 | DE   | FINING THE PROBLEM 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   | 2.1  | The Context of the Correlator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   |      | 2.1.1 Requirements due to Astronomical Objectives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   |      | 2.1.2 Requirements due to the Receiver System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   |      | 2.1.3 Requirements due to the Array Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   | 2.2  | The Type of Spectral Correlator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   | ۵.۵  | 2.2.1 The XF and FX Correlator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   | 2.3  | The GMRT Correlator - As a Black Box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   | 4.0  | The GWIRT Correlator - As a black box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3 | TH   | E DESIGN OF THE CORRELATOR 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   | 3.1  | A Bird's Eye-View of the Correlator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   |      | 3.1.1 The Flow of Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   |      | 3.1.2 Overview of Signal Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

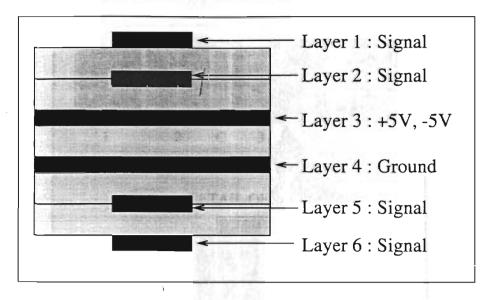

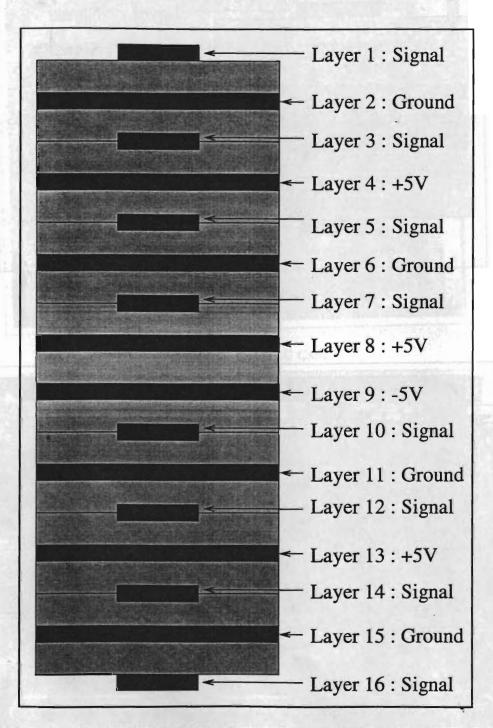

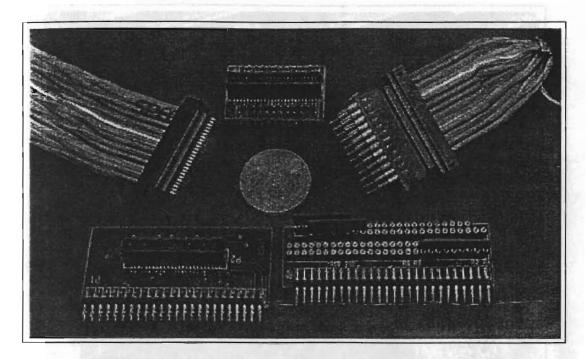

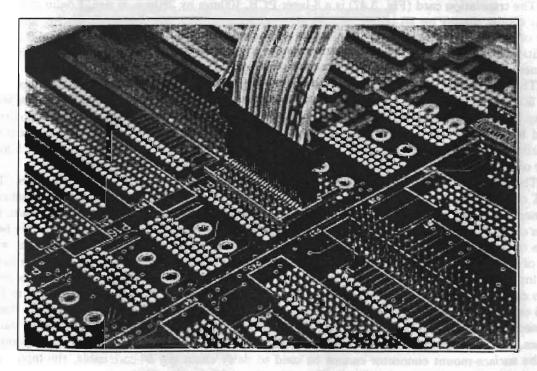

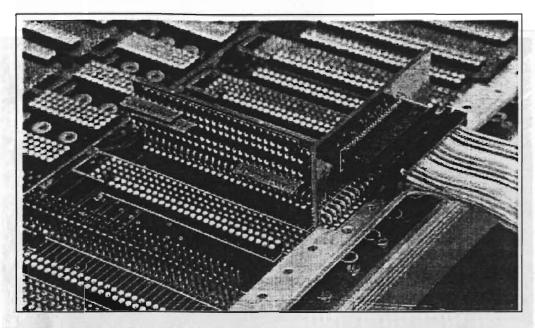

|   |      | 3.1.3 Packaging Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   | 3.2  | The Specifications of the Subsystems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   |      | 3.2.1 The ADC Subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   |      | 3.2.2 The Delay Subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   |      | 3.2.3 The FFT Subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   |      | 3.2.4 The MAC Subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   | 3.3  | The ADC Subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   |      | 3.3.1 The ADC Subsystem: Circuit Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   |      | 3.3.2 The ADC Subsystem: Packaging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

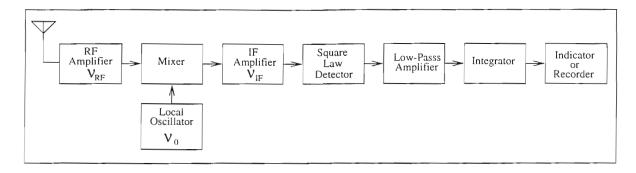

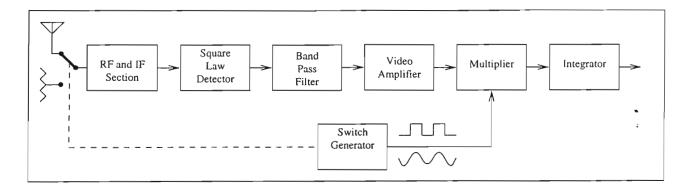

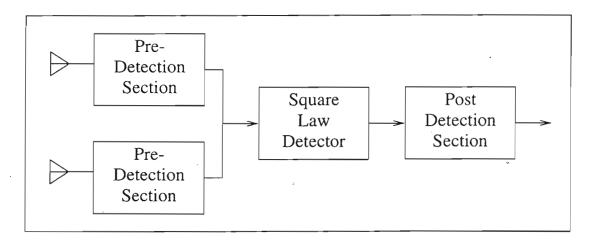

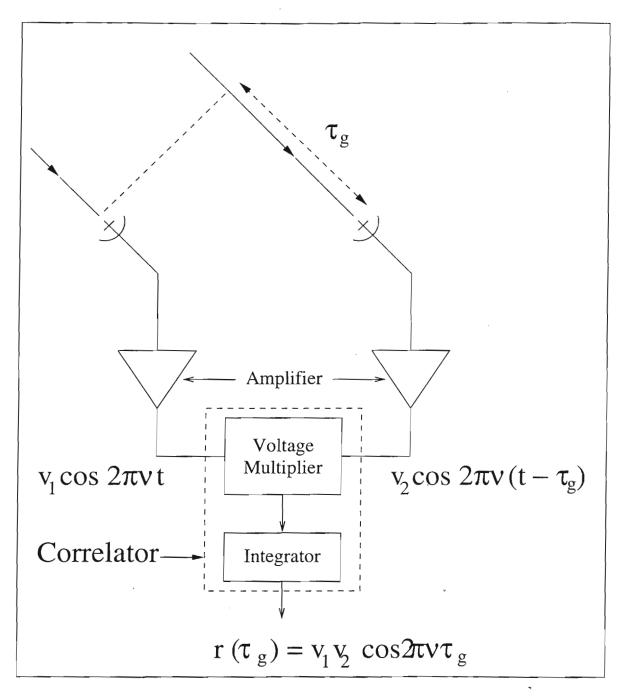

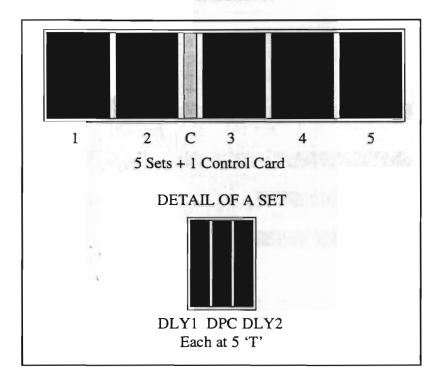

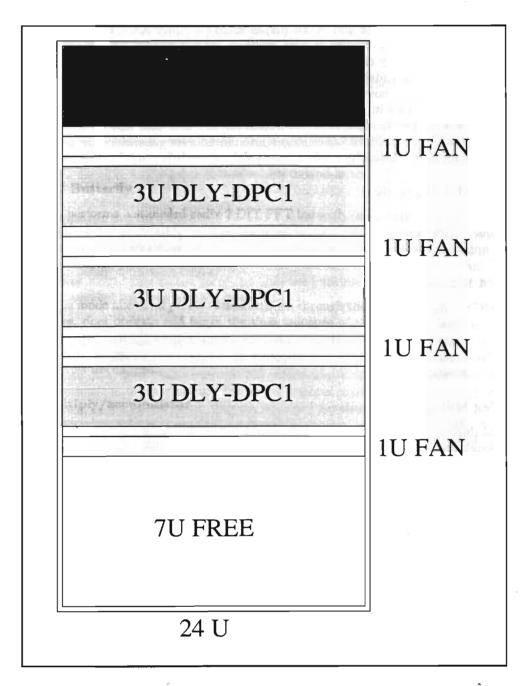

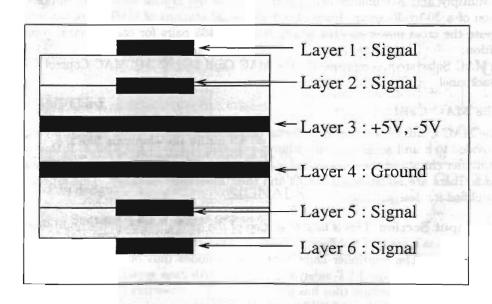

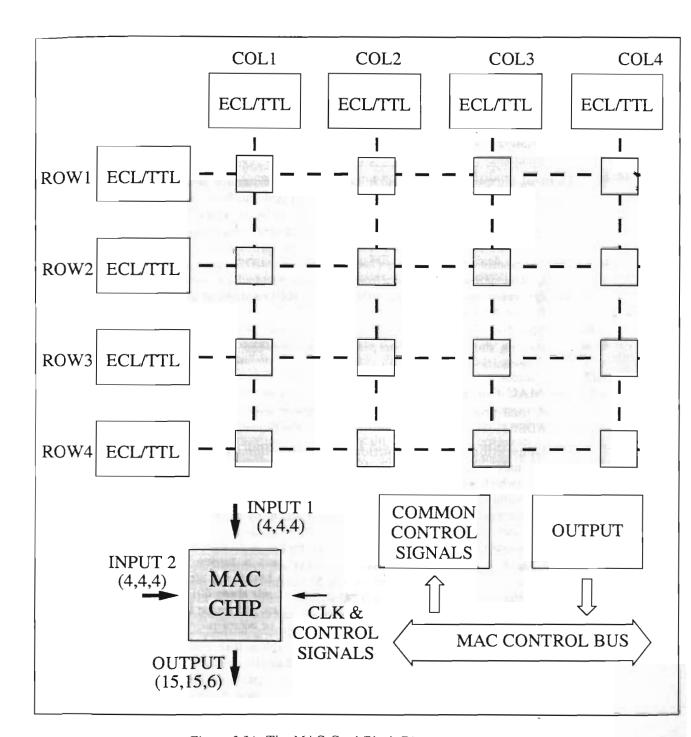

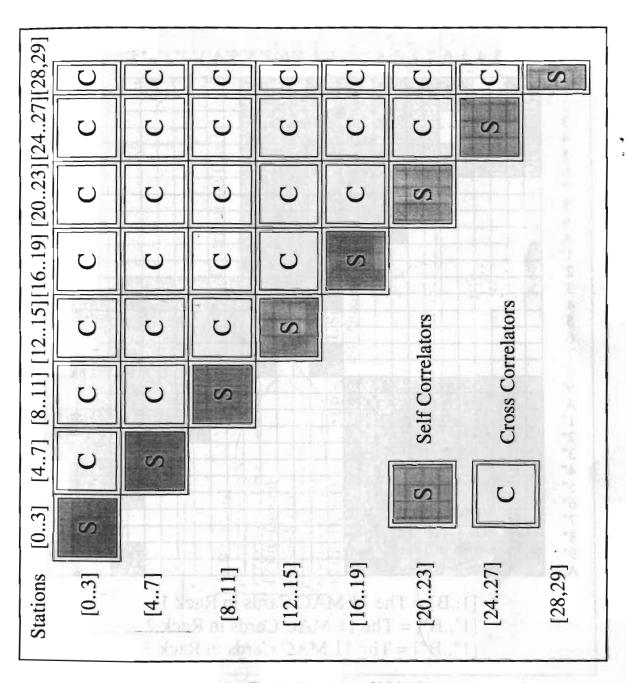

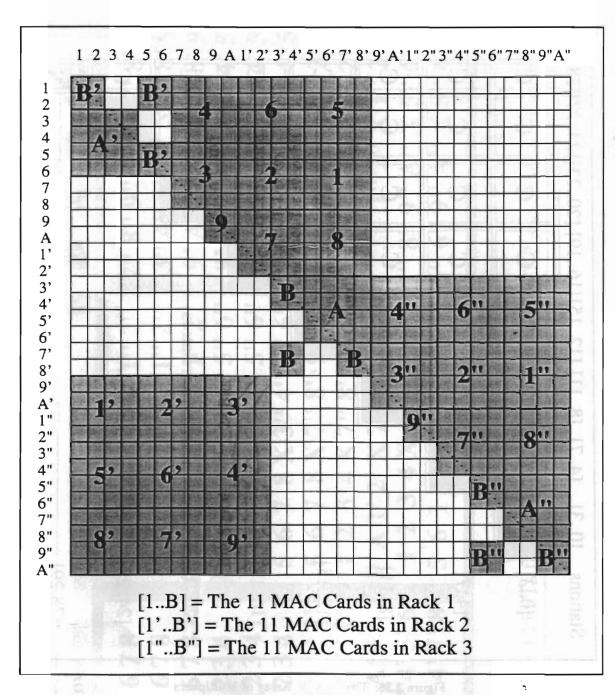

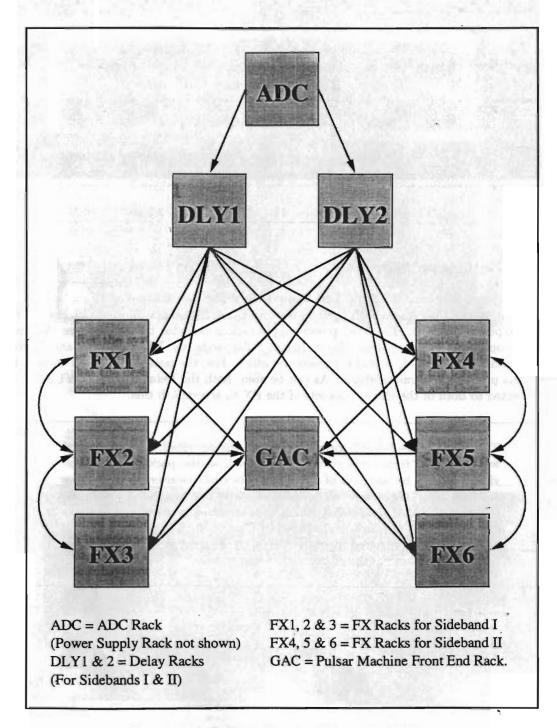

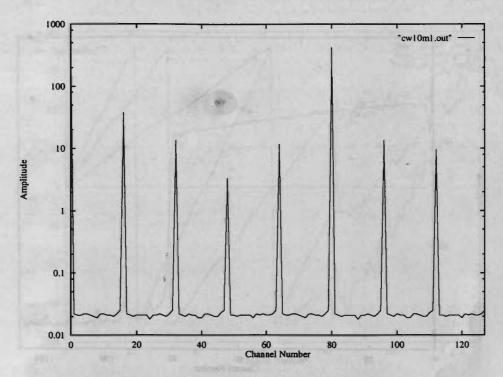

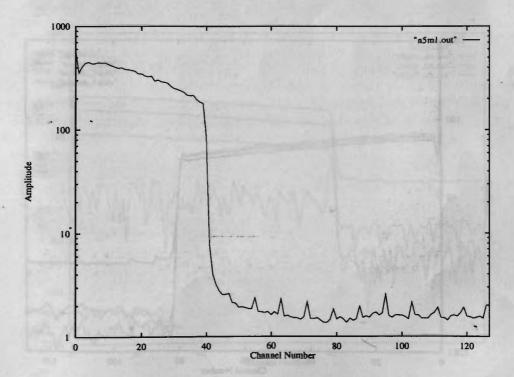

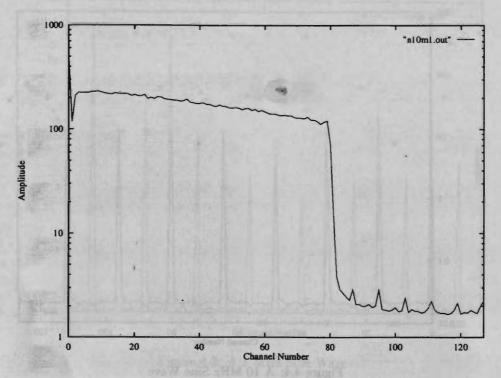

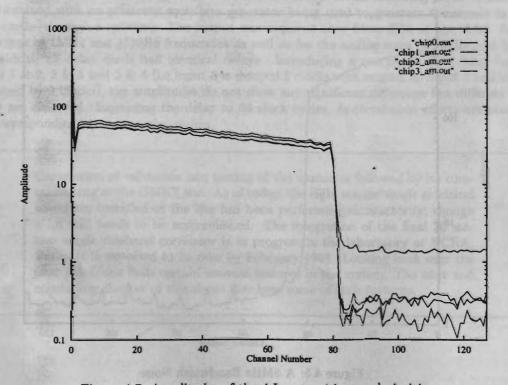

|   | 3.4  | The Delay Subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |