Α

#### **PROJECT REPORT ON**

#### COMMUNICATION BETWEEN RABBIT PROCESSOR AND PERSONAL COMPUTER USING TCP

SUBMITTED TO THE UNIVERSITY OF PUNE, IN THE PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE AWARD OF THE DEGREE

OF

#### BACHELOR OF ENGINEERING (ELECTRONICS AND TELCOMMUNICATION)

BY

NIHAR S. BENDRE PRAMESH M. SABNE AMEY A. KULKARNI B8433013 B8433084 B8433060

#### DEPARTMENT OF ELECTRONICS AND TELECOMMUNICATION

STES'S SINHGAD ACADEMY OF ENGINEERING

SINHGAD TECHNICAL EDUCATION SOCIETY

KONDHWA (BK),

**PUNE 411048**

#### CERTIFICATE

#### This is to certify that the project entitled

#### "COMMUNICATION BETWEEN RABBIT PROCESSOR AND PERSONAL COMPUTER USING TCP."

Submitted by

NIHAR S. BENDRE PRAMESH M. SABNE AMEY A. KULKARNI B8433013 B8433084 B8433060

is a bonafide work carried out by them under the supervision of Prof.C.G.Patil and it is approved for the partial fulfilment of the requirement of University of Pune for the award of the Degree of Bachelor of Engineering (Electronics and Telecommunication).

This project report is not earlier submitted to any other Institute or University for the award of any degree or diploma.

| Prof. C.G. Patil   | Dr. K.P.Patil      | Dr. A.G. Kharat |

|--------------------|--------------------|-----------------|

| Guide              | H.O.D.             | Principal       |

| Department of E&TC | Department of E&TC | SAE, Pune       |

Pune-48

Place: Pune

Date:

#### **ACKNOWLEDGEMENT**

It gives us great pleasure in presenting the project report of "COMMUNICATION BETWEEN PC AND RABBIT PROCESSOR USING TCP". With deep sense of gratitude we acknowledge the guidance of our project guide *Prof. C. G. Patil.* The time-totime assistances and encouragement by him has played a vital role in preparation and functioning of our project which helped us in completing the project work in time. We will always remain indebted to him.

We are grateful to our Principal *Dr. A.G. Kharat* and Head of Dept. *Dr. K.P. Patil*. We also take this opportunity to convey our sincere thanks to the teaching staff of Electronics and Telecommunication Dept.

Words are inadequate in offering our thanks to our Project Guide *Prof. C. G. Patil*, for his encouragement and cooperation in carrying out the project work. All our efforts and hard labour may have gone waste if we were not guided by him; he has guided us all the way and given us all his support. Besides completing such a project requires hard determination and positive energy and it is only possible if one is blessed by GOD.

It gives us a great pleasure to express my deep sense of gratitude and indebtedness to my guides **Mr. Suresh Sabhapathy** and **Mr. Abhay Bhumkar** for their valuable support and encouraging mentality throughout the project. We are highly obliged to them for providing me this opportunity to carry out their ideas and work during our project period and helping us to gain the successful completion of my Project.

We are highly grateful to the Honorable Centre Director of GMRT-NCRA, Mr. Swarnakanthi Ghosh; Chief Scientist Mr. Yashwant Gupta; and Mrs. N.S.Deshmukh, STP Coordinator, GMRT, for giving us this golden opportunity to be a part of this organization for this period.

We are also highly obliged to **Mr. J. K. Solanki**, Admin Officer D, for his support and valuable encouragement throughout my project.

Last but not the least our thanks also go to **all Admin Group**, for arranging the facility for us to make our stay at GMRT one of the most memorable period of our life.

We express our deep gratitude to all.....

NIHAR S. BENDRE PRAMESH M. SABNE AMEY A. KULKARNI (B.E, E&TC)

### **INDEX**

#### LIST OF FIGURES

#### LIST OF TABLES

| 1 |     | I     | NTRODUCTION                        | 1-13  |

|---|-----|-------|------------------------------------|-------|

|   | 1.1 |       | Background                         | 2     |

|   | 1.2 |       | History                            | 5     |

|   | 1.3 |       | Present Scenario                   | 8     |

|   | 1.4 |       | Relevance                          | 9     |

|   | 1.5 |       | Block Diagram                      | 11    |

|   |     | 1.5.1 | Proposed System                    | 11    |

|   | 1.6 |       | Structure of the Report            | 13    |

| 2 |     | SU    | URVEY                              | 14-18 |

|   | 2.1 |       | Literature Survey                  | 15    |

| 3 |     | E     | THERNET SIGNIFICANCE               | 19-31 |

|   | 3.1 |       | TCP/IP LAYERS                      | 20    |

|   |     | 3.1.1 | Link layer                         | 22    |

|   |     | 3.1.2 | Internet layer                     | 22    |

|   |     | 3.1.3 | Transport layer                    | 23    |

|   |     | 3.1.4 | Application layer                  | 24    |

|   | 3.2 |       | Ethernet Frame format              | 26    |

|   | 3.3 |       | Ethernet Address                   | 26    |

|   | 3.4 |       | Physical Connections               | 26    |

|   | 3.5 |       | Cables                             | 27    |

|   | 3.6 |       | Frames Updated                     | 28    |

|   | 3.7 |       | Collisions                         | 29    |

|   | 3.8 |       | TCP/IP Protocol Stack              | 29    |

|   | 3.9 |       | Comparison RS232, RS485 and TCP/IP | 32    |

|   |     |       |                                    |       |

| 4 |     | SYS    | TEM DESCRIPTIONS                    | 34-37 |

|---|-----|--------|-------------------------------------|-------|

|   | 4.1 |        | Design Advantages                   | 35    |

|   | 4.2 |        | Disadvantages                       | 37    |

|   | 4.3 |        | Applications                        | 37    |

| 5 |     | HAI    | RDWARE DESCRIPTION                  | 38-61 |

|   | 5.1 |        | Rabbit Module                       | 39    |

|   |     | 5.1.1  | CLOCKS                              | 41    |

|   |     | 5.1.2  | Rabbit System Management            | 41    |

|   |     | 5.1.3  | Rabbit 4000 Specifications          | 42    |

|   |     | 5.1.4  | Memory Management                   | 42    |

|   |     | 5.1.5  | Various parallel Ports              | 44    |

|   |     | 5.1.6  | Various Timers                      | 44    |

|   |     | 5.1.7  | Various Serial Ports                | 44    |

|   |     | 5.1.8  | Slave Port                          | 45    |

|   |     | 5.1.9  | DMA Channels                        | 45    |

|   |     | 5.1.10 | Pulse Width Modulation              | 46    |

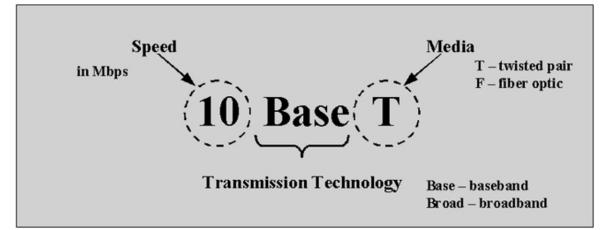

|   |     | 5.1.11 | 10BASE-T Ethernet                   | 46    |

|   | 5.2 |        | Features of Rabbit Processor        | 47    |

|   | 5.3 |        | CAT5 cable                          | 49    |

|   |     | 5.3.1  | Cable Standard                      | 49    |

|   |     | 5.3.2  | Performance of CAT5                 | 50    |

|   |     | 5.3.3  | Specifications of CAT5              | 51    |

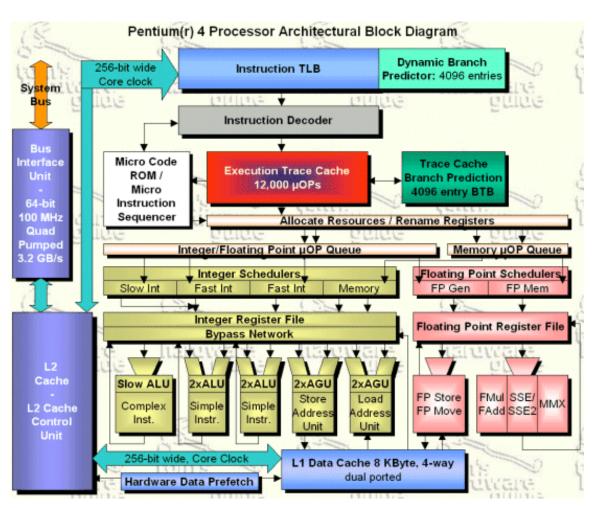

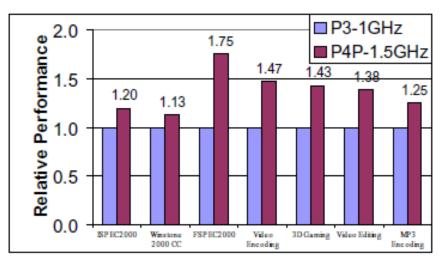

|   | 5.4 |        | Personal computer with processor P4 | 51    |

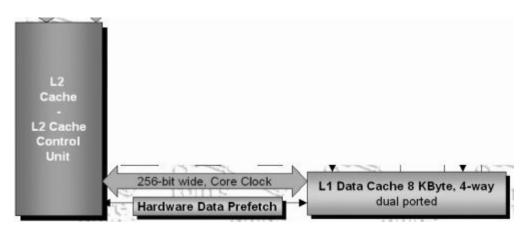

|   |     | 5.4.1  | AdvancedL2Cache                     | 54    |

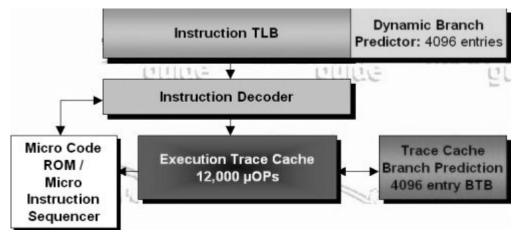

|   |     | 5.4.2  | Branch Prediction & Trace Cache     | 55    |

|   |     | 5.4.3  | Bus Interface                       | 55    |

|   |     | 5.4.4  | Instruction Decoder & Trace Cache   | 56    |

|   |     | 5.4.5  | Pipeline                            | 56    |

|   |     | 5.4.6  | Rapid Execution Engine              | 57    |

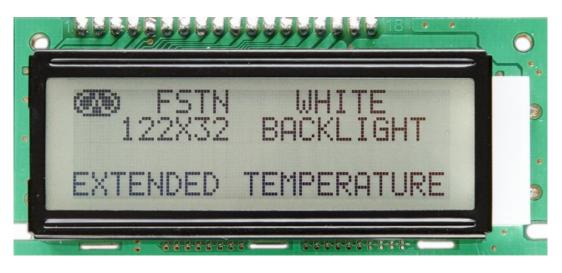

|   | 5.5 |        | LCD Display                         | 58    |

|   |     | 5.5.1  | Features                            | 58    |

|     | 5.5.2 | LCD Pin Description               | 59    |

|-----|-------|-----------------------------------|-------|

|     | 5.5.3 | Mechanical [Physical] Dimensions  | 59    |

|     | 5.5.4 | Electrical Characteristics of LCD | 60    |

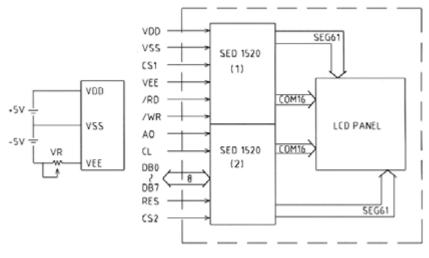

|     | 5.5.5 | Internal Block Diagram of LCD     | 60    |

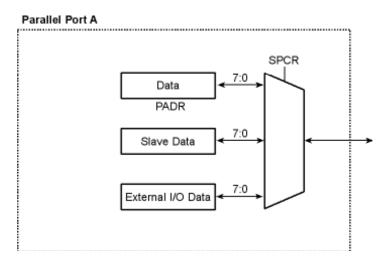

|     | 5.5.6 | Parallel Port A Interfacing       | 60    |

|     | S     | OFTWARE DESCRIPTION               | 62-71 |

| 6.1 |       | Dynamic C                         | 63    |

|     | 6.1.1 | Nature of Dynamic C               | 63    |

|     | 6.1.2 | Speed                             | 64    |

|     | 6.1.3 | New Features from ANSI C          | 64    |

|     | 6.1.4 | Enhancements of Dynamic C         | 65    |

|     | 6.1.5 | Different keywords in Dynamic C   | 67    |

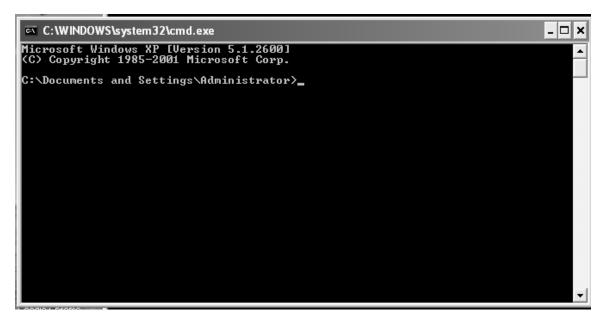

| 6.2 |       | Command Prompt                    | 70    |

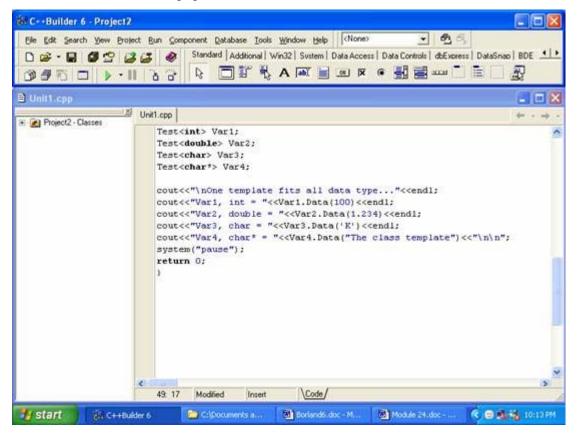

| 6.3 |       | Borland C                         | 70    |

|     | S     | YSTEM PERFORMANCE EVALUATION      | 72-85 |

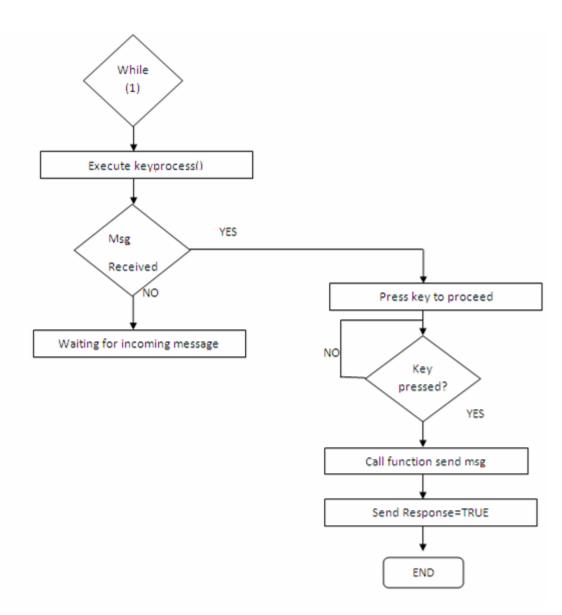

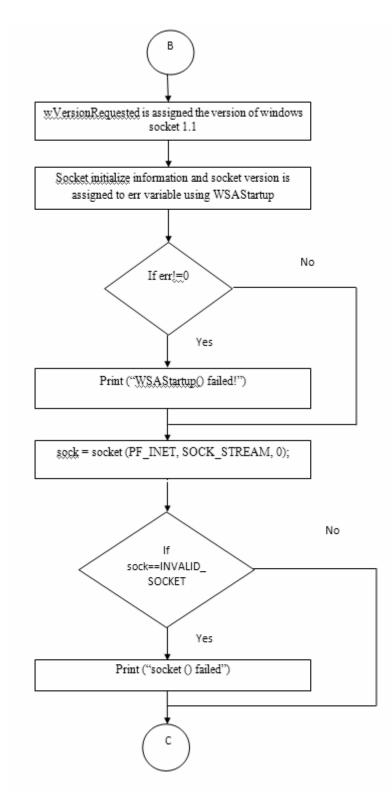

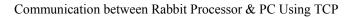

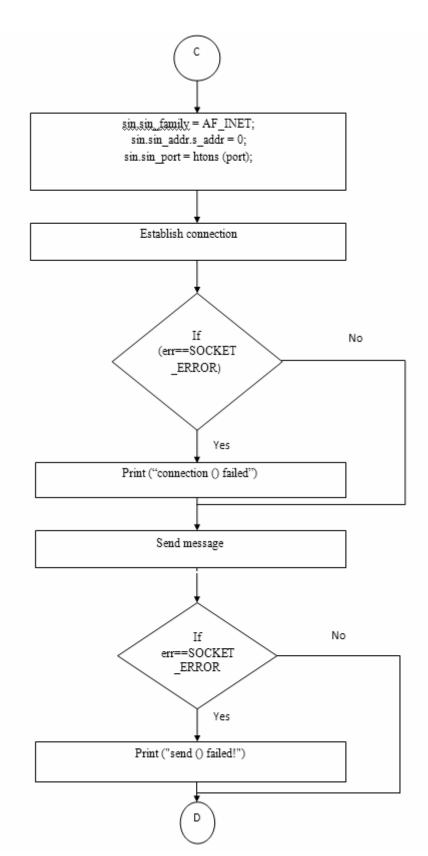

| 7.1 |       | [Receiver Section] Algorithm      | 73    |

|     | 7.1.1 | Main Program                      | 73    |

|     | 7.1.2 | Functions                         | 74    |

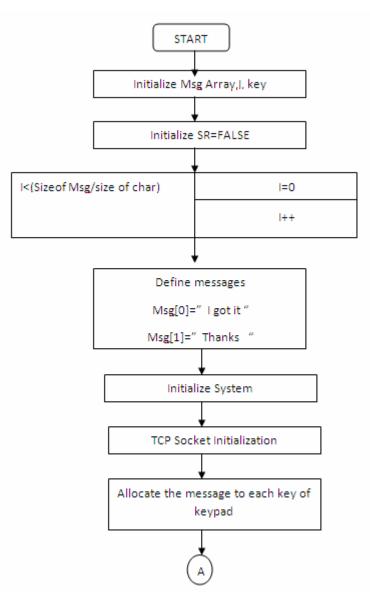

| 7.2 |       | Flowchart                         | 75    |

|     | 7.2.1 | Main Program                      | 75    |

|     | 7.2.2 | Functions                         | 77    |

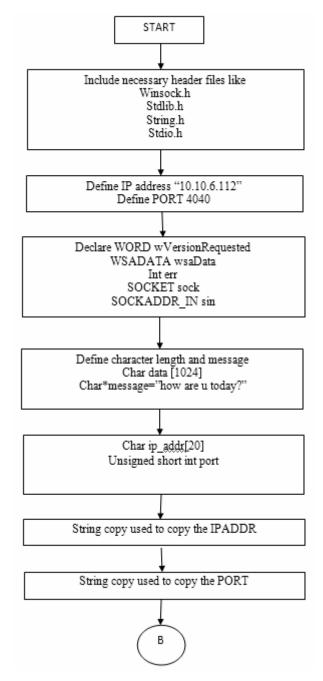

| 7.3 |       | [Transmitter Section] Algorithm   | 78    |

|     | 7.3.1 | Main Program                      | 78    |

| 7.4 |       | Flowchart                         | 80    |

|     | 7.4.1 | Main Program                      | 81    |

| 7.5 |       | Problems faced and solution       | 84    |

| 8  |     | FUTURE SCOPE               | 86-87 |

|----|-----|----------------------------|-------|

|    | 8.1 | Future Expansion and Scope | 87    |

| 9  |     | SYSTEM COSTING             | 88-89 |

|    | 9.1 | Total Cost                 | 89    |

| 10 |     | CONCLUSION                 | 90-91 |

|    |     | REFERENCES                 | 92-93 |

|    |     | PUBLICATIONS               | 94-95 |

### **LIST OF FIGURES**

| Figure Number                       | FIGURE DESCRIPTION                                        | Page Number |

|-------------------------------------|-----------------------------------------------------------|-------------|

| Figure 1                            | Function of GMRT Servo System                             | 3           |

| Figure 2                            | Block Diagram Present System                              | 8           |

| Figure 3                            | Block Diagram of Proposed System I                        | 11          |

| Figure 4                            | Block Diagram of Proposed System II (3- D)                | 12          |

| Figure 5                            | Illustration of TCP                                       | 20          |

| Figure 6                            | TCP layer & functions                                     | 25          |

| Figure 7                            | Ethernet Frame format old                                 | 26          |

| Figure 8                            | Ethernet Network                                          | 27          |

| Figure 9                            | Ethernet Frame format updated                             | 28          |

| Figure 10                           | Flow of Data Between Two Computers Using<br>TCP/IP Stacks | 30          |

| Figure 11                           | TCP/IP Protocol Flow                                      | 31          |

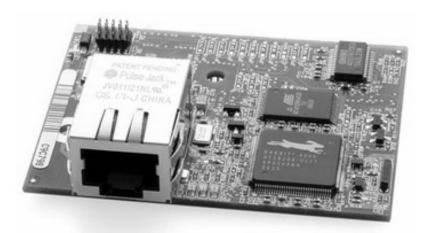

| Figure 12                           | Rabbit 4000 Module with 4300 Processor                    | 39          |

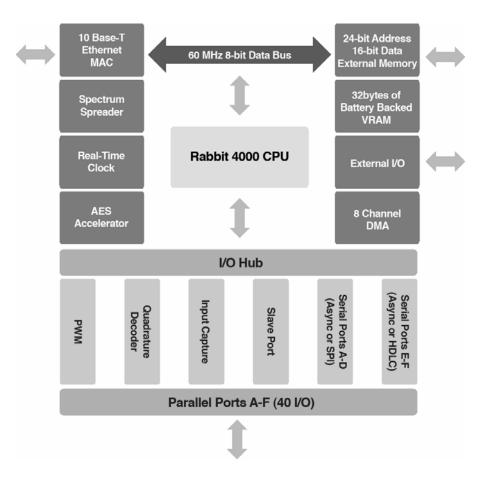

| Figure 13                           | Rabbit 4000 CPU Block Diagram                             | 40          |

| Figure 14                           | Rabbit 4000 Specifications                                | 42          |

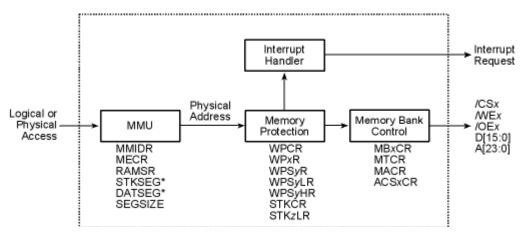

| Figure 15                           | Memory Management in Rabbit Processor                     | 43          |

| Figure 16                           | CAT 5 Cable                                               | 49          |

| Figure 17                           | Performance of CAT 5                                      | 50          |

| Figure 18                           | Meaning of 10BaseT [Transmission Technology]              | 50          |

| Figure 19   Specifications of CAT 5 |                                                           | 51          |

| Figure 20 | Pentium 4 Block Diagram               | 53 |

|-----------|---------------------------------------|----|

| Figure 21 | Performance comparison of P4 with P3  | 54 |

| Figure 22 | Advanced L2 Cache of P4               | 54 |

| Figure 23 | Branch Prediction & Trace Cache of P4 | 55 |

| Figure 24 | Bus Interface of P4                   | 55 |

| Figure 25 | Instruction Decoder & Trace Cache     | 56 |

| Figure 26 | Pipelining in P4                      | 56 |

| Figure 27 | Rapid Execution Engine                | 57 |

| Figure 28 | LCD 122x32 Display                    | 58 |

| Figure 29 | Internal Block Diagram of LCD         | 60 |

| Figure 30 | Parallel Port A in Rabbit Processor   | 61 |

| Figure 31 | General Dynamic C example             | 66 |

| Figure 32 | Dynamic C Look                        | 69 |

| Figure 33 | Command Prompt Look                   | 70 |

| Figure 34 | Borland C look                        | 71 |

| Figure 35 | Main Program Flow Rx I                | 75 |

| Figure 36 | Main Flow Rx II                       | 76 |

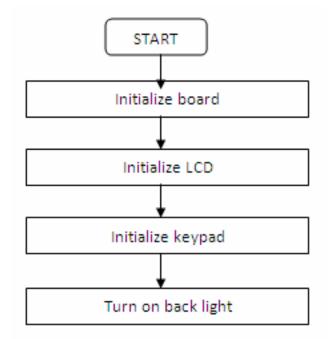

| Figure 37 | Subroutine Rx [ System Initialize]    | 77 |

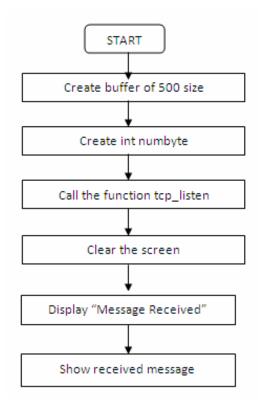

| Figure 38 | Subroutine Rx [Receive Message]       | 77 |

| Figure 39 | Flowchart Tx I                        | 80 |

| Figure 40 | Flowchart Tx II                       | 81 |

| Figure 41 | Flowchart Tx III                      | 82 |

| Figure 42 | Flowchart Tx IV                       | 83 |

### **LIST OF TABLES**

| Table NumberTable Description |                                      | Page Number |  |

|-------------------------------|--------------------------------------|-------------|--|

| 1                             | <b>Operating Frequencies of GMRT</b> | 5           |  |

| 2                             | QDR (Quad Data Rate) of P4           | 53          |  |

| 3                             | LCD 122x 32 Pin Descriptions         | 59          |  |

| 4                             | Physical Dimensions of LCD           | 59          |  |

| 5                             | Electrical Characteristics of LCD    | 60          |  |

| 6                             | System Costing                       | 89          |  |

Communication between Rabbit Processor & PC Using TCP

# <u>CHAPTER 1 -</u>

## **INTRODUCTION**

SAOE ELECTRONICS AND TELECOMMUNICATION ENGINEERING 2011-12

#### 1.1 Background-

The Tata Institute of Fundamental Research (TIFR) has set up two major radio astronomy facilities during the past 3-4 decades. One is at Ooty, about 300 kms south west of Bangalore; the second one is at Khodad, about 80 Kms north of Pune and about 100 Kms east of Mumbai (Bombay). While Ooty radio telescope has been in operation for the past 35 years, The Giant Metrewave Radio Telescope (GMRT) is a new facility commissioned in 2001, near Pune. We describe GMRT briefly and the solar observations being made with it.

Two major radio astronomy facilities of TIFR are at Ooty (ORT) and at Khodad (GMRT). While ORT has been in operation for 35 years, GMRT was opened as an international facility since 2001. We briefly describe only GMRT here.

The Giant Metre-wave Radio Telescope (GMRT) is a mammoth instrument for studying astrophysical phenomena at low radio frequencies (40 to 1600 MHz). This has been built in India by NCRA-TIFR as a national project at a cost of about 15 million US \$ (1992). • The array telescope consists of 30 antennas of 45 metres diameter, each, operating at metre wavelengths -- the largest in the world at these frequencies!

#### Location and Configuration of the GMRT-

- ✓ Latitude : 19 deg N

- ✓ Longitude : 74 deg E

- ✓ About 70 km N of Pune

- ✓ 100 km E of Mumbai.

- ✓ 30 dishes; 45 m diameter

- ✓ 12 dishes in central compact array

- ✓ Remaining along 3 arms of a Y-array

- ✓ Total extent: 14 km radius, resolution of a 25 km size antenna is achieved!

#### Some important sub-systems of the GMRT-

- ✓ Mechanical sub-system

- ✓ <u>Servo sub-system</u>

- ✓ Antenna feeds (including positioning & control)

- ✓ Receiver chain -- analog

- ✓ Optical fibre sub-system

- ✓ Receiver chain -- digital

- ✓ Telemetry sub-system

- ✓ "On-line" Control and Monitor sub-sytem

- ✓ Off-line data processing chain(s)

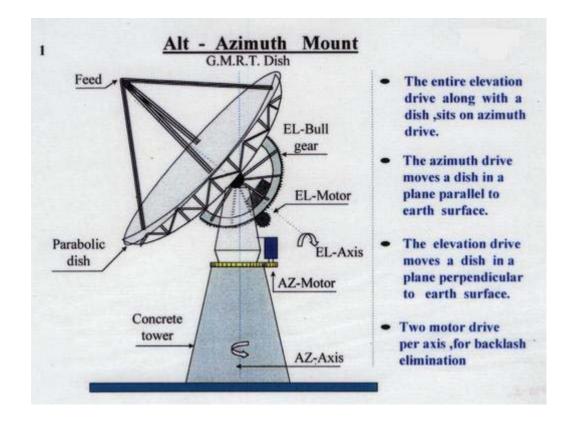

**SERVO System** of GMRT controls and monitors the movement of the 30 antennas in Azimuth and Elevation. We all know that there 30 fully steerable parabolic dishes of 45 metre diameter each at GMRT. Motion of these gaint antennas need to be controlled by a precession control system. Pointing of the antennas should be accurate i.e. the radio source, antenna focused and the antenna center should be aligned. The GMRT servo system has designed with three nested control loops to achive the pointing accuracy of (1 or 2) arc minutes RMS for wind speed less than 20 km/ph. Because of high weight alt-azimuth mount is most favorable approach for positioning the dish antenna. Here the elevation axis sits on the azimuth drive. The elevation drive moves antenna up and down directions while azimuth drive moves antenna in clockwise & counter-clockwise direction. Hence, enabling the antenna to point anywhere in the sky. There are also various specifications of Servo System at GMRT such as Dish Mount – Dish Movement – Dish speed specifications, Operating Voltage specification, Design and Survival wind speed specification, etc.

Figure 1 Function of GMRT Servo System

SAOE ELECTRONICS AND TELECOMMUNICATION ENGINEERING 2011-12

Communication between Rabbit Processor & PC Using TCP

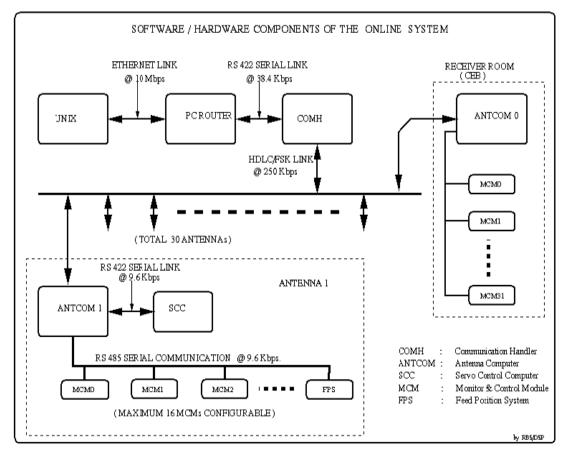

Some key features of the Control and Monitor Systems are-

1) The rotation of all the thirty antennas in AZIMUTH and ELEVATION through SERVO CONTROL COMPUTER (SCC).

Azimuth--> -270 TO +270 deg Elevation --> 17 TO 90 deg

--> Using ABC - SERVO RS422 communication link @ 9.6 Kbps.

2) Alignment of the required feed for observation to the focus of the dish thro' Feed Position System (FPS).

0 deg --> 233/610 MHz 90 deg --> 150 MHz 180 deg --> 1420 MHz 270 deg --> 325 MHz

--> Using ABC - FPS RS485 communication link @ 9.6 Kbps.

3) Selection of FRONT END SYSTEM parameters like observing freq. band, Noise Cal, Channel Swap etc through MCM '5' & MCM - FE interface card in the Common Box.

4) Sets the LO Freq., IF bandwidth (6,16,32 MHz), IF attn., ALC ON/OFF etc. using MCM-s '2', '3' & '9' located in LO/IF SYSTEM

5) Sets Baseband bandwidth (62.5 kHz to 16 MHz) using MCM-s located in BASEBAND SYSTEM through Antcom '0'.

6) Monitors the C & M system parameters at Antenna shell using MCM '0' at NRR and at CEB using 6 MCM-s through Antcom '31'.

7) Monitors the Temperature at various points in RFI cage in each antenna through Temperature Monitor system using MCM '0'.

In addition, it also provides the vital voice communication link between CEB & all the Antennas i.e. You can contact anybody in any antenna using C & M SYSTEM.

The communication medium is a single mode analog optical fibre link operating  $\langle a \rangle$ 1310 nm between CEB and all the antennas i.e. two fibres are available for each antenna. So, the digital command & control signals are converted to analog form using non-coherent FSK techniques and sent along with the LO and IF signals. In the forward link, Telemetry command signals are combined with the LO carriers and transmitted to all the antennas and in the return link, Telemetry monitor signals are

combined with the IF signals and brought to CEB. The FORWARD link uses 18 MHz carrier & the RETURN link uses 205.5 MHz.

#### **Operating Frequencies of GMRT-**

The operating frequencies of GMRT are as follows,

| SERIAL NUMBER | FREQUENCIES  |

|---------------|--------------|

| 1             | 40-60MHz     |

| 2             | 120-180MHz   |

| 3             | 225-245MHz   |

| 4             | 300-360MHz   |

| 5             | 580-650MHz   |

| 6             | 1000-1430MHz |

Table 1 Operating Frequencies of GMRT

#### Science with GMRT-

- ✓ Sun and Solar System astronomy

- ✓ Study and discovery of Pulsars

- ✓ Studies of Galactic Centre regions

- ✓ Discovery of organic molecules like Acetaldehyde

- ✓ Nearby galaxies, Dwarf Galaxies, etc

- ✓ Peculiar radio galaxies

- ✓ Red shifted hydrogen line studies

- ✓ Gamma Ray bursters, etc.

#### 1.2 History-

**Rabbit Semiconductor** is the company which designs and sells the Rabbit family of microcontrollers and microcontroller modules. For development, it provides Dynamic C, a non-standard dialect of C with proprietary structures for multitasking. Rabbit Semiconductor was formed expressly to design a better microprocessor for use in small- and medium-scale single-board computers. The first microprocessors were the *Rabbit 2000* and the *Rabbit 3000*. The latest microprocessor is the *Rabbit 4000*. Rabbit microprocessor designers have had years of experience using Z80, Z180, and HD64180 microprocessors in small single-board computers. The

SAOE ELECTRONICS AND TELECOMMUNICATION ENGINEERING 2011-12

Rabbit microprocessors share a similar architecture and a high degree of compatibility with these microprocessors, but represent a vast improvement.

Rabbit Semiconductor was purchased in 2006 by Digi International. Before the purchase, Rabbit Semiconductor was a division of Z-World, Inc. Z-World developed and manufactured embedded controller products as well as embedded software development environments.

Giant Metrewave Radio Telescope (GMRT), located near Pune in Maharashtra, India, is the world's largest array of radio telescopes at metre wavelengths. It is operated by the National Centre for Radio Astrophysics, administered by Tata Institute of Fundamental Research, Mumbai. A huge antenna dish (like the antenna that the cable-operator has on his roof) is moving atop a stationary structure. It is not a mean task for a 45 metre antenna to move mechanically. It is awesome. It is beautiful. Stretching my eyes over the horizon, I saw few more antenna - all tilting together searching for a common goal. Located on the quite and isolated of Pune, is Khodad (near Narayangaon) where I'm standing. What I'm watching is the Giant Metrewave Radio Telescope (GMRT) of the Tata Institute of Fundamental Research, Mumbai the world's largest radio telescope. It consists of thirty45-m dishes arranged in a Y-shaped configuration spread over distances of ~25 km. Work on GMRT was started ~ 1989 under the leadership of Prof. Govind Swarup and by 1996, all the 30 antennas were operational. The telescope is being used by astronomers from all over the world to study and learn more about astronomical objects emitting in radiofrequencies. GMRT works in the radio regime where the wavelength is of the light is order of a metre (the wavelength of the red light that you see is about a million times smaller than a metre). There are number of astronomical objects which emit mainly in the radio wavelengths but only the powerful emitters can be detected since these objects are very distant. One of the science projects of GMRT is to detect hydrogen from very distant galaxies. Hydrogen forms a major constituent of our Universe from which galaxies are formed. Atomic hydrogen emits radio emission at 21 cm. It is believed that the Universe is expanding and the distant galaxies are moving away further from us. GMRT was a huge project, and a lot of research went into it. Interestingly, the wired net used to make the antenna-dishes is an innovative technology by the Indian engineers. GMRT is one of the most challenging experimental programmes in basic sciences undertaken by the Indian

SAOE ELECTRONICS AND TELECOMMUNICATION ENGINEERING 2011-12

scientists and engineers. The antennas have stopped moving and started collecting radio waves from the source.

**Borland C++** is a C and C++ programming environment (that is, an integrated development environment) for MS-DOS and Microsoft Windows. It was the successor to Turbo C++, and included a better debugger, the Turbo Debugger, which was written in protected mode DOS.

Object Windows Library (OWL): A set of C++ classes to make it easier to develop professional graphical Windows applications.

Turbo Vision: A set of C++ classes to create professional applications in DOS. Those classes' mimics some of the aspects of a Windows application like: dialog boxes, messages pumps, menus, accelerators, etc.

Version History-

- ✓ Borland C++ 2.0 (1991, <u>MS-DOS</u>)

- ✓ Borland C++ 3.0 (1991) new compiler support to build Microsoft Windows applications.

- ✓ Borland C++ 3.1 (1992) Introduction of Windows-based IDE and application frameworks (OWL 1.0, Turbo vision 1.0)

- ✓ Borland C++ 4.0 (1993, Windows 3.x) MS-DOS <u>IDE</u> supported no longer, included OWL 2.0.

- ✓ Borland C++ 1.0 (1992, <u>OS/2</u>)

- ✓ Borland C++ 1.5 (?, <u>OS/2</u>)

- ✓ Borland C++ 2.0 (1993, <u>OS/2</u>) Support for 2.1 and Warp 3. OWL 2.0. Included IBM SMART Toolset for automatically migrating Windows applications to OS2. Last version.

- ✓ Borland C++ 4.01

- ✓ Borland C++ 4.02 (1994)

- ✓ Borland C++ 4.5

- ✓ Borland C++ 4.51

- ✓ Borland C++ 4.52 (1995) Official support for Windows 95, OWL 2.5

- ✓ Borland C++ 4.53

- ✓ Borland C++ 5.0 (1996, Windows 95) Released in March 1996. Works on Windows 95 and Windows NT 3.51. It does not (officially) work on Windows

NT 4.0 (which was still in development at that time). 3rd party tests exhibited some problems on NT 4.0. It does not work in Windows 3.x or DOS. Despite that, it can produce Win32, Win16 or DOS programs.

- ✓ Borland C++ 5.01

- ✓ Borland C++ 5.02 (1997) Final independent release of the Borland C++ IDE (subsequently replaced up by the <u>C++Builder</u> series), final release to support compilation to (real-mode) MS-DOS target. Windows NT 4.0 officially supported.

- ✓ Borland C++ Builder 4.0 + Borland C++ 5.02 (1999) Bundle combination to facilitate the migration to C++Builder.

- ✓ Borland C++ 5.5 Command-line compiler only (not with IDE).

#### 1.3 Present Scenario-

Figure 2 Block Diagram Present System

The system is under development, present system of GMRT is based on Microcontroller 8051 and Microprocessor 8086. Here the serial communication between  $\mu$ c8051 and  $\mu$ p8086 is implemented by following the protocol RS232. So by using RS232 protocol of serial communication provides low data transfer speed.

At the base of each antenna there is one control room and one microprocessor 8086 card. The function of the up 8086 is to accept the instruction from uc 8051 to rotate the corresponding Servo Motor connected to antenna. Microcontroller 8051s are connected to each of up8086 and all the uc8051s are connected to one central control room at the main building. If any Astronaut wants to rotate antenna for certain angle for his observations, then he conveys his message to people in the telemetry sections. the telemetry section send the control The people from signal to uc8051.Microcontroller 8051 will receive the control message and take control action to send message to up8086. Then up8086 will receive that message and send control signal to servo motor to rotate the motor in the desired angle. Whole communication is done by following the serial communication protocol RS232.

#### 1.4 Relevance-

The effective and efficient communication encounters the problems such as supported data rate, interfacing with the various electrical machines, compatibility with the new devices and existing protocols, difficulties in soft programming, etc. *Giant Metrewave Radio Telescope, National Centre for Radio Astrophysics, Tata Institute of Fundamental Research, Pune* has decided to upgrade their present Communication System to overcome these limitations.

TIFR has set up a unique facility for radio astronomical research using the metrewavelengths range of the radio spectrum, known as the Giant Metrewave Radio Telescope (GMRT). GMRT consists of 30 fully steerable gigantic parabolic dishes of 45m diameter each spread over distances of up to 25 km. GMRT aims to search for and study rapidly-rotating Pulsars in our galaxy and is one of the most challenging experiments for Indian scientists.

GMRT Khodad, Narayangaon is a well known research institute. It is a joint venture of Tata Institute of Fundamental Research and the Govt. of India. The institute specializes in the research in the field of Astronomy and Astrophysics. It is frequently visited by Scientists all over the world. This has the facility to tune antennas to observe

galaxies, pulsars, quasars etc at certain altitude. This is done by focusing the antenna to the required altitude, continuous scanning of frequencies and processing of data. Hence the system should support very high data rate. But protocols implemented in the present system are based on old technologies; therefore, the data rate is low. It has been decided to use TCP instead of serial protocols such as RS232, RS422, and RS485 because of supported data rate, and compatibility with the new devices. Also when programming the processors likes  $\mu$ c8051 and  $\mu$ p80186, assembly language programming gets difficult and very lengthy.

The present system is working continuously in the Dynamic environment i.e. depending on the requirement of Scientists. The electrical machines like motors, etc have to be interfaced with the processors to control the rotation of motors and ultimately antennas. It is often seen that while interfacing the newly introduced electrical machine to the present system, system fails to support. Therefore, it has been decided to upgrade system by using the Rabbit processors which overcome the above discussed problems like low supported data rate, interfacing with the various electrical machines, compatibility with the new devices and existing protocols, difficulties in soft programming, as programming language for the processor is 'C'.

The Rabbit Semiconductor was established majorly to design a better microprocessor for use in small- and medium-scale single-board computers. The Rabbit microprocessors share a similar architecture and a high degree of compatibility with current Microprocessors but show much better performance. The Rabbit 4000 is a high performance microprocessor with low electromagnetic interference (EMI), and is designed specifically for embedded control, communications, and network connectivity. Extensive integrated features and glueless architecture facilitate rapid hardware design, while a C-friendly instruction set promotes efficient development of even the most complex applications.

#### 1.5 Block Diagram-

#### 1.5.1 Proposed System

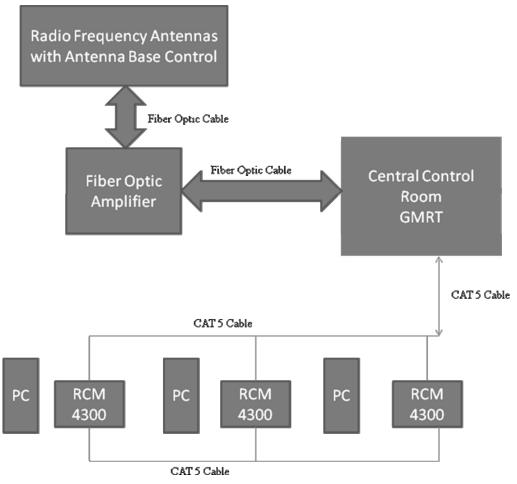

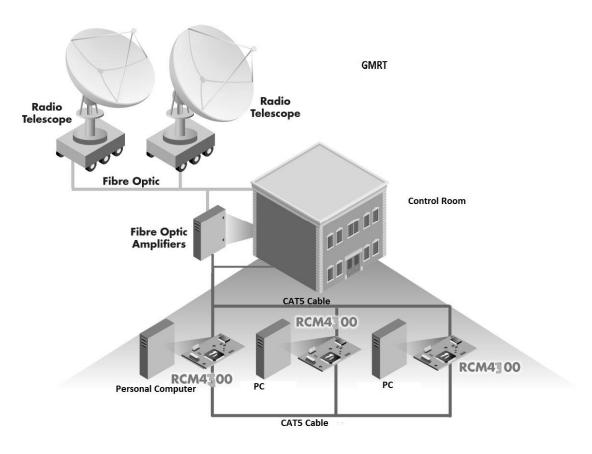

Figure 3 Block Diagram of Proposed System I

Here the devices like Personal Computer, RCM4300 are the main devices in the system. Role of personal computer are to send the instruction to RCM4300 processor. The programmer will decide the instruction for RCM4300 for each task.CAT5 cable (Ethernet Cable) is used as a transmission line which connects PC to RCM4300.Here the Personal Computer which we are using has Pentium 4(P4) processor inside. As we have RCM4300 processor which supports 10BaseT Ethernet, means it supports Ethernet of 10Mbps, so we are using CAT5 cable.CAT5 cable which also called as LAN cable is also capable of supporting this much speed.RCM4300 is the heart of the system, which accepts the instructions from PC, interprets them and takes corresponding control action on the instructions. So it will be configured as Transreceiver, as it receives the signal from PC and send control signal to other

devices. For better understanding of the block diagram, we have created the same diagram in 3-D as well.

Figure 4 Block Diagram of Proposed System II (3- D)

#### 1.6 Organization of the Report -

The remaining report is organized as, chapter [2] proceeds with the Literature Survey. Chapter [3] explains Ethernet Significance; it includes TCP layers, function of each layer in TCP, connection, frame formats and comparison of TCP with other protocols like RS 232 and RS 485, etc. Chapter [4] discusses System Description; it includes advantages of proposed system using Rabbit as well as TCP, also discuses the drawbacks and some of the applications.

The Hardware Description is explained in Chapter [5] which includes brief description about hardware components required to design this system like Rabbit 4000 Module, CAT 5 cable, Personal computer. Also performance comparison and specifications of CAT 5 cable are mentioned. Software Description is elaborated in Chapter [6]; it includes all the required software for this system like Dynamic C, Borland C, and Command Prompt. System Performance Evaluation is discussed in Chapter [7] which includes Flows of Transmitter and Receiver along with the problems faced while designing this system with their solution.

Chapter [8] explains Future scope of the system and chapter [9] tells the total costing of the system. Chapter [10] concludes the paper and at last References are mentioned from where we took help to design the system.

Communication between Rabbit Processor & PC Using TCP

# <u>CHAPTER 2 - SURVEY</u>

#### 2.1 Literature Survey-

The architecture of this system is useful in a number of different areas. The literature survey for this system started from collecting the information about the existing systems for based on Rabbit Processors. We then divided the whole architecture in different blocks and studied each separately. We divided the system architecture like two of our group members will study the ports, registers present on the Rabbit Processor, and 1 group member will study related to TCP/IP, how to initiate Ethernet in the Rabbit.

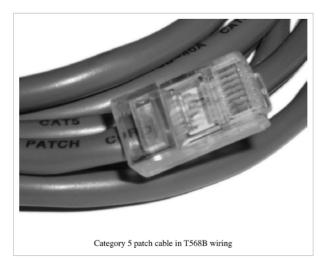

The basic study included: The study of present GMRT system, the study of Rabbit Processor, TCP/IP [Ethernet protocol], how to initiate this protocol in the Rabbit Processor, study of Dynamic C, Borland C, and study of CAT5 cable and how to make it cross or straight, etc.

The present system of GMRT is based on Microcontroller 8051 and Microprocessor 8086. Here the serial communication between  $\mu$ c8051 and  $\mu$ p8086 is implemented by following the protocol RS232. So by using RS232 protocol of serial communication provides low data transfer speed.

The problems faced by GMRT are supported data rate, interfacing with the various electrical machines, compatibility with the new devices and existing protocols, difficulties in soft programming, etc. Hence, there is a need of upgradation.

Selection criteria for Rabbit Processor are, the Rabbit Semiconductor was established majorly to design a better microprocessor for use in small- and mediumscale single-board computers. The Rabbit microprocessors share a similar architecture and a high degree of compatibility with current Microprocessors but show much better performance. The Rabbit 4000 is a high performance microprocessor with low electromagnetic interference (EMI), and is designed specifically for embedded control, communications, and network connectivity. Extensive integrated features and glueless architecture facilitate rapid hardware design, while a C-friendly instruction set promotes efficient development of even the most complex applications. For the study of TCP/IP, we used the reference book viz. *Behrouz A Forouzan*, "*Data Communications and Networking*", *Third Edition, McGraw Hill Publication*. This book gave us the brief introduction of Data communication and Networking takes place through TCP. It also helped in studying TCP layers in details.

The Transmission Control Protocol (TCP) is one of the core protocols of the Internet Protocol Suite. TCP is one of the two original components of the suite, complementing the Internet Protocol (IP), and therefore the entire suite is commonly referred to as TCP/IP. TCP provides reliable, ordered delivery of a stream of bytes from a program on one computer to another program on another computer. TCP is the protocol that major Internet applications such as the World Wide Web, email, remote administration and file transfer rely on. Other applications, which do not require reliable data stream service, may use the User Datagram Protocol (UDP), which provides a datagram service that emphasizes reduced latency over reliability. The TCP/IP model is a descriptive framework for computer network protocols created in the 1970s by DARPA, an agency of the United States Department of Defense. The name derives from the two most important protocols of the networking protocol suite, the Transmission Control Protocol (TCP) and the Internet Protocol (IP). The model evolved from the operational principles of the ARPANET, which were an early wide area network and a predecessor of the Internet. The TCP/IP model is formalized in the Internet protocol suite and is sometimes called the Internet model or the Do D model.

The TCP/IP model describes a set of general design guidelines and implementations of specific networking protocols to enable computers to communicate over a network. TCP/IP provides end-to-end connectivity specifying how data should be formatted, addressed, transmitted, routed and received at the destination. Protocols exist for a variety of different types of communication services between computers.

TCP/IP has four abstraction layers as defined in RFC 1122. This layer architecture is often compared with the seven-layer OSI model; using terms such as *Internet reference model*, incorrectly, however, because it is descriptive while the OSI model was intended to be prescriptive, hence being a reference model.

The TCP/IP model and related protocols are maintained by the Internet Engineering Task Force (IETF).

For the study of **Rabbit 4000**, we used *Rabbit 4000 User Manual*. The Rabbit processor family shares many features with the <u>Zilog Z80/Z180</u> processors. For example, the <u>registers</u> of a Rabbit 2000/3000 processor are almost the same as the registers of a Z80/Z180 processor. The Rabbit 4000 processor expands to include the use of 32-bit registers. The <u>instruction set</u> of Rabbit processors also closely resembles the instruction set of the Z80/Z180 family. While the opcodes of many instructions are the same between the Rabbit 2000/3000 processors and Z80/Z180 processors, the two families of processors are not binary compatible.

The Rabbit processor family has unique features. For example, the Z80/Z180 family disables <u>interrupts</u> once an interrupt is serviced by an interrupt service routine. However, the Rabbit processors permit interrupts to interrupt service routines according to priorities (a total of 4). As with the Z80/Z180 family, the Rabbit processors are <u>CISC</u> processors, as opposed to <u>RISC</u> competitors like the <u>Atmel AVR</u> processors. A comparison of clocks per instruction of the Rabbit processor against a typical RISC processor like the AVR reveals that even though the Rabbit processors can use a faster clock (up to 60MHz), the effective processing power is comparable to that of a similarly-priced AVR processor using a slower clock (up to 32MHz). For example, the "INC (IX+d)" instruction requires 12 clocks on a Rabbit processor. The equivalent instruction sequence (LDD, INC, STD) on an AVR requires 5 cycles. Another example is the *CALL* instruction. It requires 12 cycles on a Rabbit processor versus 4 to 5 cycles on an AVR processor. This difference, in part, is due to the AVR using on-chip memory for both instructions and data.

For the study of Dynamic C, we used *Dynamic C Function Reference Manual*. Dynamic C is an integrated development system for writing embedded software. It is designed for use with Rabbit controllers and other controllers based on the Rabbit microprocessor. Perhaps the most notable feature of the Rabbit microcontroller is its development environment. Dynamic C, a product of Rabbit Semiconductor, has additions, deletions and inconsistencies compared to the ANSI-C standard. (Reference: Porting a Program to Dynamic C-Rabbit Semiconductor)

**Dynamic C** follows the ISO/ANSI C standard when feasible and desirable. Because the standard does not take into account the special needs of embedded systems, it is necessary to depart from the standard in some areas and desirable in others. The standard does not take into account important embedded systems issues such as read only memory and embedded assembly language. For this reason, practical compilers intended for embedded systems do not completely comply with the standard, but use it as a guide.

Rabbit Semiconductor claims that the instruction set of Rabbit processors is optimized for C code A similar claim is made by Atmel for their AVR processors. The two architectures actually have very similar addressing modes, such as literal, register, indirect and indirect plus displacement. Furthermore, both architectures have specialized 16-bit registers. The Rabbit has the IX, IY and SP, whereas the AVR has X, Y and Z.

The main difference is that the Rabbit instructions place more constraints on register usage compared to the AVR instructions. For example, the 8-bit Rabbit *ADD* instruction permits only the A-register be the destination. However, the *ADD* instruction of the AVR permits the use any one of the 32 8-bit registers as the source or destination. Generally speaking, an instruction set that is less register restrictive is more optimizable because there is less need to save-and-reload the content of a register.

We also studied the software like Borland C; it creates one type of Graphical User Interface which is based on MS Dos. It is common platform for Embedded Systems; it works on most of the Embedded ICs.

The books viz. Embedded Ethernet and Internet Complete Designing and Embedded Systems Design using the Rabbit 3000 Microprocessor interfacing, networking and application development are used how to write the programs for TCP stack in the Rabbit Processors and also used to study sample programs of Rabbit Processor.

So by this way we have completed our study part and started working on the actual project and programming of Rabbit.

### CHAPTER 3 -

### **ETHERNET**

# **SIGNIFICANCE**

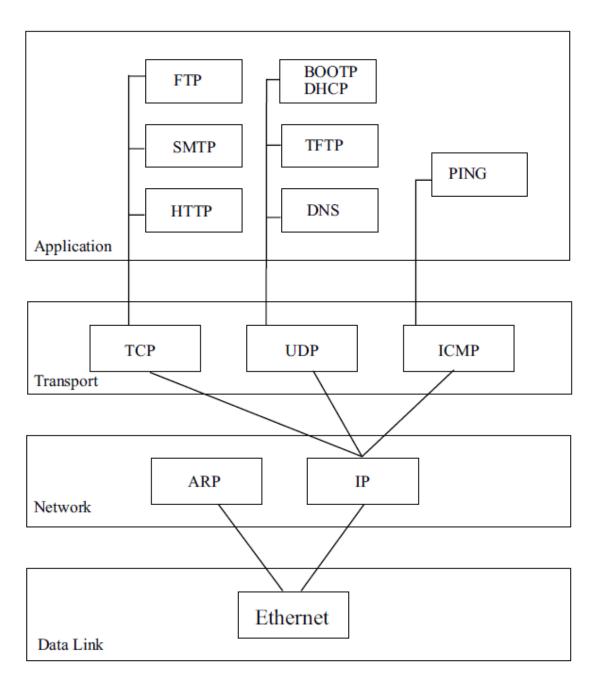

#### **3.1 TCP/IP LAYERS**

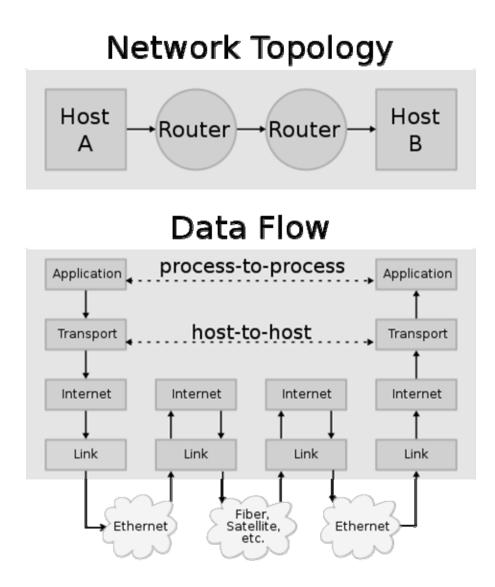

#### **Figure 5 Illustration of TCP**

The layers near the top are logically closer to the user application, while those near the bottom are logically closer to the physical transmission of the data. Viewing layers as providing or consuming a service is a method of abstraction to isolate upper layer protocols from the nitty-gritty detail of transmitting bits over, for example, Ethernet and collision detection, while the lower layers avoid having to know the details of each and every application and its protocol.

This abstraction also allows upper layers to provide services that the lower layers cannot, or choose not to, provide. Again, the original OSI model was extended to include connectionless services (OSIRM CL). For example, IP is not designed to be

reliable and is a best effort delivery protocol. This means that all transport layer implementations must choose whether or not to provide reliability and to what degree. UDP provides data integrity (via a checksum) but does not guarantee delivery; TCP provides both data integrity and delivery guarantee (by retransmitting until the receiver acknowledges the reception of the packet).

This model lacks the formalism of the OSI model and associated documents, but the IETF does not use a formal model and does not consider this a limitation, as in the comment by David D. Clark, "We reject: kings, presidents and voting. We believe in: rough consensus and running code." Criticisms of this model, which have been made with respect to the OSI model, often do not consider ISO's later extensions to that model.

- For multiaccess links with their own addressing systems (e.g. Ethernet) an address mapping protocol is needed. Such protocols can be considered to be below IP but above the existing link system. While the IETF does not use the terminology, this is a subnetwork dependent convergence facility according to an extension to the OSI model, the internal organization of the network layer (IONL).

- ICMP & IGMP operate on top of IP but do not transport data like UDP or TCP. Again, this functionality exists as layer management extensions to the OSI model, in its *Management Framework*(OSIRM MF)

- The SSL/TLS library operates above the transport layer (uses TCP) but below application protocols. Again, there was no intention, on the part of the designers of these protocols, to comply with OSI architecture.

- 4. The link is treated like a black box here. This is fine for discussing IP (since the whole point of IP is it will run over virtually anything). The IETF explicitly does not intend to discuss transmission systems, which is a less academic but practical alternative to the OSI model.

The following is a description of each layer in the TCP/IP networking model starting from the lowest level.

#### 3.1.1 Link layer-

The link layer is the networking scope of the local network connection to which a host is attached. This regime is called the *link* in Internet literature. This is the lowest component layer of the Internet protocols, as TCP/IP is designed to be hardware independent. As a result TCP/IP is able to be implemented on top of virtually any hardware networking technology.

The link layer is used to move packets between the Internet layer interfaces of two different hosts on the same link. The processes of transmitting and receiving packets on a given link can be controlled both in the software device driver for the network card, as well as on firmware or specialized chipsets. These will perform data link functions such as adding a packet header to prepare it for transmission, and then actually transmit the frame over a physical medium. The TCP/IP model includes specifications of translating the network addressing methods used in the Internet Protocol to data link addressing, such as Media Access Control (MAC), however all other aspects below that level are implicitly assumed to exist in the link layer, but are not explicitly defined.

This is also the layer where packets may be selected to be sent over a virtual private network or other networking tunnel. In this scenario, the link layer data may be considered application data which traverses another instantiation of the IP stack for transmission or reception over another IP connection. Such a connection, or virtual link, may be established with a transport protocol or even an application scope protocol that serves as a tunnel in the link layer of the protocol stack. Thus, the TCP/IP model does not dictate a strict hierarchical encapsulation sequence.

#### 3.1.2 Internet layer-

The internet layer has the responsibility of sending packets across potentially multiple networks. Internetworking requires sending data from the source network to the destination network. This process is called routing.

In the Internet protocol suite, the Internet Protocol performs two basic functions:

- *Host addressing and identification*: This is accomplished with a hierarchical addressing system (see IP address).

- *Packet routing*: This is the basic task of sending packets of data (datagrams) from source to destination by sending them to the next network node (router) closer to the final destination.

IP can carry data for a variety of different upper layer protocols. These protocols are each identified by a unique protocol number: for example,Internet Control Message Protocol (ICMP) and Internet Group Management Protocol (IGMP) are protocols 1 and 2, respectively.

Some of the protocols carried by IP, such as ICMP (used to transmit diagnostic information about IP transmission) and IGMP (used to manage IP Multicast data) are layered on top of IP but perform internetworking functions. This illustrates the differences in the architecture of the TCP/IP stack of the Internet and the OSI model.

#### 3.1.3 Transport layer-

The responsibility of the transport layer includes end-to-end message transfer independent of the underlying network, along with error control, segmentation, flow control, congestion control, and application addressing (port numbers). End to end message transmission or connecting applications at the transport layer can be categorized as connection-oriented, implemented in TCP, or connectionless, implemented in UDP.

The transport layer can be thought of as a transport mechanism, e.g., a vehicle with the responsibility to make sure that its contents (passengers/goods) reach their destination safely and soundly, unless another protocol layer is responsible for safe delivery. The transport layer provides this service of connecting applications through the use of service ports. Since IP provides only a best effort delivery, the transport layer is the first layer of the TCP/IP stack to offer reliability. IP can run over a reliable data link protocol such as the High-Level Data Link Control (HDLC). Protocols above transport, such as RPC, also can provide reliability.

For example, the TCP is a connection-oriented protocol that addresses numerous reliability issues to provide a reliable byte stream:

- data arrives in-order

- data has minimal error (i.e. correctness)

- duplicate data is discarded

- lost/discarded packets are resent

- includes traffic congestion control

The newer Stream Control Transmission Protocol (SCTP) is also a reliable, connection-oriented transport mechanism. It is message-stream-oriented — not byte-

stream-oriented like TCP — and provides multiple streams multiplexed over a single connection. It also provides multi-homing support, in which a connection end can be represented by multiple IP addresses (representing multiple physical interfaces), such that if one fails, the connection is not interrupted. It was developed initially for telephony applications (to transport SS7 over IP), but can also be used for other applications.

User Datagram Protocol is a connectionless datagram protocol. Like IP, it is a best effort, "unreliable" protocol. Reliability is addressed through error detection using a weak checksum algorithm. UDP is typically used for applications such as streaming media (audio, video,Voice over IP etc.) where on-time arrival is more important than reliability, or for simple query/response applications like DNS lookups, where the overhead of setting up a reliable connection is disproportionately large. Real-time Transport Protocol (RTP) is a datagram protocol that is designed for real-time data such as streaming audio and video.

TCP and UDP are used to carry an assortment of higher-level applications. The appropriate transport protocol is chosen based on the higher-layer protocol application. For example, the File Transfer Protocol expects a reliable connection, but the Network File System (NFS) assumes that the subordinate Remote Procedure Call protocol, not transport, will guarantee reliable transfer. Other applications, such as VoIP, can tolerate some loss of packets, but not the reordering or delay that could be caused by retransmission. The applications at any given network address are distinguished by their TCP or UDP port. By convention certain *well known ports* are associated with specific applications.

#### 3.1.4 Application layer-

The application layer contains the higher-level protocols used by most applications for network communication. Examples of application layer protocols include the File Transfer Protocol (FTP) and the Simple Mail Transfer Protocol (SMTP). Data coded according to application layer protocols are then encapsulated into one or (occasionally) more transport layer protocols (such as TCP or UDP), which in turn use lower layer protocols to effect actual data transfer. Since the IP stack defines no layers between the application and transport layers, the application layer must include any protocols that act like the OSI's presentation and session layer protocols. This is usually done through libraries.

Application layer protocols generally treat the transport layer (and lower) protocols as black boxes which provide a stable network connection across which to communicate, although the applications are usually aware of key qualities of the transport layer connection such as the end point IP addresses and port numbers. As noted above, layers are not necessarily clearly defined in the Internet protocol suite. Application layer protocols are most often associated with client-server applications, commoner servers have specific and the ports assigned to them by the IANA: HTTP has port 80; Telnet has port 23; etc. Clients, on the other hand, tend to use ephemeral ports, i.e. port numbers assigned at random from a range set aside for the purpose.

Transport and lower level layers are largely unconcerned with the specifics of application layer protocols. Routers and switches do not typically "look inside" the encapsulated traffic to see what kind of application protocol it represents; rather they provide conduit for it. However, some firewall and bandwidth just a throttling applications do try to determine what's inside, as with the Resource Reservation Protocol (RSVP). It's also sometimes necessary for Network Address Translation (NAT) facilities to take account of the needs of particular application layer protocols. (NAT allows hosts on private networks to communicate with the outside world via a single visible IP address using port forwarding, and is an almost ubiquitous feature of modern domestic broadband routers).

|         | Name of Layer                                   | Purpose of Layer                                       |

|---------|-------------------------------------------------|--------------------------------------------------------|

| Layer 5 | Application                                     | Specifies how a particular application uses a network. |

| Layer 4 | Transport                                       | Specifies how to ensure reliable transport of data.    |

| Layer 3 | 3 Internet Specifies packet format and routing. |                                                        |

| Layer 2 | Network                                         | Specifies frame organization and transmittal.          |

| Layer 1 | Physical                                        | Specifies the basic network hardware.                  |

Figure 6 TCP layer & functions

#### 3.2 Ethernet Frame format-

| Preamble | Destination<br>Address | Source<br>Address | DATA   | CRC |

|----------|------------------------|-------------------|--------|-----|

| 8 bytes  | 6                      | 6                 | 0-1500 | 4   |

#### Figure 7 Ethernet Frame format old

TCP/IP (Transmission Control Protocol/Internet Protocol) is a set of protocols independent of the physical medium used to transmit data, but most data transmission for Internet communication begins and ends with Ethernet frames.

The Ethernet can use either a bus or star topology. A bus topology attaches all devices in sequence on a single cable. In a star topology all devices are wired directly to a central hub. 10Base-T uses a combination called a star-shaped bus topology because while the attached devices can share all data coming in on the cable, the actual wiring is in a star shape.

The access method used by the Ethernet is called Carrier Sense Multiple Access with Collision Detect (CSMA/CD). This is a contention protocol, meaning it is a set of rules to follow when there is competition for shared resources.

#### 3.3 Ethernet Address-

All Ethernet interfaces have a unique 48-bit address that is supplied by the manufacturer. It is called the Ethernet address (also known as the MAC address, for Media Access Control). Ethernet-enabled Rabbit boards store this value in Flash Memory (EEPROM) that is programmed at the factory. If you need unique Ethernet addresses for some product you are making, you can obtain them from the IEEE Registration Authority.

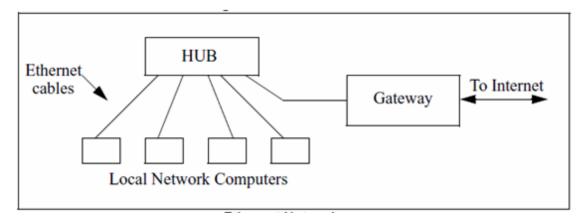

#### **3.4 Physical Connections-**

A Realtek RTL8019 10Base-T interface chip provides a 10 Mbps Ethernet connection. This chip is used on many Ethernet-enabled Rabbit boards. The corresponding port can be connected directly to an Ethernet network.

By using hubs and routers, a network can include a large number of computers. A network might include all the computers in a particular building. A local network can be

connected to the Internet by means of a gateway. The gateway is a computer that is connected both to the local net work and to the Internet. Data that must be sent out over the Internet are sent to the local network interface of the gateway, and then the gateway sends them on to the Internet for routing to some other computer in the world. Data coming in from the Internet are directed to the gateway, which then sends them to the correct recipient on the local network.

## 3.5 Cables-

Ethernet cables are similar to U.S. telephone plug cables, except they have eight connectors. For our purposes, there are two types of cables—crossover and straight-through. In most instances, the straight-through cables are used. It is necessary to use a crossover cable when two computers are connected directly without a hub (for example, if you want to connect your PC's Ethernet directly to the Rabbit Semiconductor TCP/IP Development Board.) Some hubs have one input that can accept either a straight-through or crossover cable depending on the position of a switch. In this case make sure that the switch position and cable type agree.

**Figure 8 Ethernet Network**

SAOE ELECTRONICS AND TELECOMMUNICATION ENGINEERING 2011-12

27

# 3.6 Frames Updated-

| Ethernet Frame    |                                       |  |  |  |

|-------------------|---------------------------------------|--|--|--|

| 62 bits           | Preamble used for bit synchronization |  |  |  |

| 2 bits            | Start of Frame Delimiter              |  |  |  |

| 48 bits           | Destination Ethernet Address          |  |  |  |

| 48 bits           | Source Ethernet Address               |  |  |  |

| 16 bits           | Length or Type                        |  |  |  |

| 46 -1500<br>bytes | Data                                  |  |  |  |

| 32 bits           | Frame Check Sequence                  |  |  |  |

|                   |                                       |  |  |  |

### Figure 9 Ethernet Frame format updated

Bits flowing across the Ethernet are grouped into structures called frames. A frame must be between 46 and 1500 bytes in size. An Ethernet frame has four parts:

✓ A Preamble of 8 bytes that helps synchronize the circuitry, thus allowing small bit rate differences between sender and receiver.

$\checkmark$  A Header of 14 bytes that contains a 6 byte destination address, 6 byte source address and a 2 byte type field.

$\checkmark$  A Data area of variable length that, along with the header, is passed to the IP layer (the Network layer).

✓ A Trailer of 4 bytes that contains a CRC to guard against corrupted frames.

If the destination address is all 1 bits, it defines a broadcast frame and all systems on the local network process the frame. There are also multicast frames. A subset of systems can form a "multicast" group that has an address that does not match any other system on the network. All systems in a particular subset process a packet with a destination address that matches their subset. A system can belong to any number of subsets. A system may put its interface(s) into promiscuous mode and process all frames sent across its Ethernet. This is known as "sniffing the ether." It is used for network debugging and spying.

#### 3.7 Collisions-

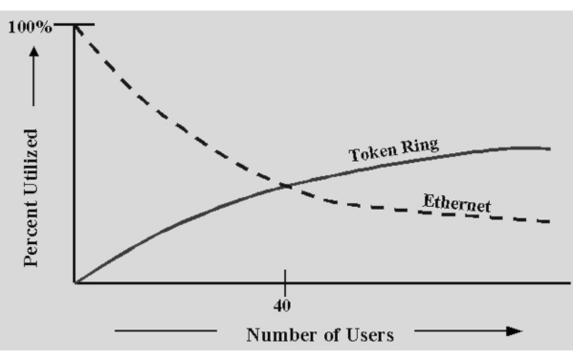

In a star-shaped bus topology, all systems have access to the network at any time. Before sending data, a system must determine if the network is free or if it is already sending a frame. If a frame is already being sent, a system will wait. Two systems can "listen" on the network and "hear" silence and then proceed to send data at the same time. This is called a collision. Ethernet hardware has collision detection sensors to take care of this problem. This is the Collision Detect (CD) part of CSMA/CD. The colliding data is ignored, and the systems involved will wait a random amount of time before resending their data.

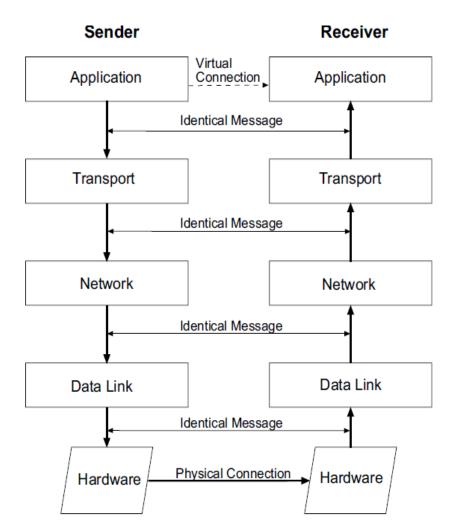

## 3.8 TCP/IP Protocol Stack-

TCP/IP is the protocol suite upon which all Internet communication is based. Different vendors have developed other networking protocols, but even most network operating systems with their own protocols, such as Netware, support TCP/IP. It has become the de facto standard.

Protocols are sometimes referred to as protocol stacks or protocol suites. A protocol stack is an appropriate term because it indicates the layered approach used to design the networking software.

Communication between Rabbit Processor & PC Using TCP

Figure 10 Flow of Data Between Two Computers Using TCP/IP Stacks

Each host or router in the internet must run a protocol stack. The details of the underlying physical connections are hidden by the software. The sending software at each layer communicates with the corresponding layer at the receiving side through information stored in headers. Each layer adds its header to the front of the message from the next higher layer. The header is removed by the corresponding layer on the receiving side.

Figure 11 TCP/IP Protocol Flow

#### 3.9 Comparison RS232, RS485 and TCP/IP-

RS232: One master and one slave. Typically a cable with 3 conductors with max length of approx a couple of hundred feet. Usually easy. Sometimes some jumpers are required at one end to defeat handshaking. RS-232 is point-to-point only and short distance, typically 20m. Not generally useful for 'multiple dispensers' without multiple serial ports and associated protocol and application software. RS485: One master and up to 128 slaves but take care to read more if you plan on more than 32. There are two wiring systems - so called 2-wore and so called 4-wire. They can be incompatible but usually 4-wire devices can be made to work on 2-wire systems. Each device must have a unique address and all devices must be set to the same baud rate, data bits, stop bits and parity. Usually easy to implement. The RS485 physical layer allows up to 128 devices to be installed on a single network with a max physical length of 4000ft and speeds up to 115k baud. Using repeaters allows the length to be increased. Compare to Ethernet where the spec allows a max of 100 meters (330ft) on a single unrepeated segment.

Distances to 1000m, rates dependent on distance, can range from the low hundreds/Kb at long distance to 1.5Mb at short distances, daisy chain/multidrop topology, balanced differential line to common mode bias but subject and issues. TCP/IP: All devices are essentially peers. A single device can be a master and a server. Routers can be used to connect sub-nets together. Broadcasts are almost ever used so are not an issue. 100m distance, rates to 100Mb or 1 GB, hub and spoke topology, transformer coupled signals minimizes common mode issues.

### The noticeable differences are-

RS-485 can have a "bus" type multi-drop connection (multiple connections to the same cable), while modern Ethernet uses a "hub" type connection. While that sounds like an advantage for RS-485, a "hub and spoke" installation is often a lot easier in practice when you look at where you will run the cables. You can typically run a single Ethernet cable out to a switch located at a cluster of nodes, and then run another cable from that switch out to another switch at another cluster of nodes, etc. There's a limit to how many "hops" you can do that for, but whether that is a problem in practice depends on your physical layout. RS-485 wiring and termination problems are a routine question that we get here, so the problems with RS-485 are probably quite common. Ethernet seems to be less prone to installation problems. However, if you are not using off the shelf Ethernet cables, make sure the wiring contractor connects the right wires to the right pins! They can sometimes hook it up wrong and things will still mostly work. The problems usually relate to mixing and matching wires from different pairs instead of keeping the pairs together.

"Serial servers" or "terminal servers" are a common way of connecting serial devices over Ethernet, so you can often use serial devices with Ethernet. If you are running you're wiring a long distance outdoors, then you might want to look at fiber optic cable, as that may give you better resistance to lightning.

If I was putting in a new installation today and I had a choice, I would prefer Ethernet and TCP/IP over RS-485. I suspect that RS-485 will eventually disappear from the market, while I expect Ethernet to be around for a very long time to come. Communication between Rabbit Processor & PC Using TCP

# CHAPTER 4 - SYSTEM **DESCRIPTION**

## 4.1 Design Advantages-

- ✓ Designed for embedded networking with intelligence and I/O control

- ✓ Serves web pages, controls remote devices, links equipment to the Internet Security-key feature with encryption capabilities adds peace of mind for OEMs and systems integrators

- ✓ Complete microprocessor, on-board memory, development software with royalty-free TCP/IP stack, and hundreds of sample programs reduce time-to-market

Rabbit Semiconductor provides low-cost, quick-to-market solutions for a variety of networked embedded systems. Rabbit's RabbitCore microprocessor core modules and customizable single-bard computer solutions offer fast and powerful development solutions with a variety of form factors, I/O configurations, and memory. These solutions are used in building security, point of sale, parking systems, telecommunications, vehicle and ship systems, container tracking and a broad variety of similar applications. Rabbit bundles hardware and software together, creating an engineer-friendly development environment.

✓ Glueless architecture of Rabbit 4000

Glue-less means that no other silicon is necessary to connect the processors together. For example, The Nehalem EX with four full QPI can support glue-less 8-way system architecture. Each processor connects directly to all seven other processors with a half-wide QPI link, and uses the remaining half wide QPI to connect to the IOH.

The "glue" people refer to are those chips with a few gates in them. Glue-less means that there is no need to invert or buffer or whatever the odd signal here and there. All has been thought out. These chips are also called jelly bean chips sometimes. Getting rid of them is good for many reasons, including reduced cost in volume applications.

#### ✓ Generates low EMI of just 25dBµV

As microprocessor speeds increase, reducing Electromagnetic Interference (EMI) becomes an essential part of design considerations. This application note provides guidelines to aid the PC desktop system and motherboard designer with low cost solutions on reducing EMI. The document focuses on the efforts made by Rabbit Semiconductors to prevent systems utilizing Rabbit Semiconductors processors and components from interfering with other electronic products. There are generally two methods by which interference is measured:

• below 30 MHz EMI RF, noise is measured as conducted emissions

• above 30 MHz RF, noise is measured as *radiated* emissions.

As all of the frequencies generated for and by the P6 class of microprocessor (e.g., Pentium<sup>®</sup> III processor, Pentium<sup>®</sup> II processor, Rabbit Semiconductors<sup>®</sup> 4000, and Pentium<sup>®</sup> Pro processor) exceed 50 MHz, this document concerns itself only with radiated emissions above 50 MHz

- ✓ Supports 10BaseT Ethernet

- ✓ Memory Organization and Compiling Program

In time of compiling the Program which one has written at Dynamic C, one has a choice of doing his or her software development in the flash memory or in the Static RAM included on the RCM4000. The Flash Memory and SRAM options are selected with the OPTIONS > PROGRAM OPTION > COMPILER menu. The Advantage of working in RAM is to save wear the flash memory, which is limited to about 100,000 write cycles. The Disadvantage is that the code and data might not both fit in RAM. An operation can be compiled in RAM, but cannot run standalone from RAM after the programming cable is disconnected. All standalone applications can run only from flash memory.

## ✓ Standard Debugging Features

There are lots of standard debugging features in Dynamic C which help user to make understood what is happening in time of running of any programming. Those features are:

1. Breakpoints: Set breakpoints that can disable interrupts.

- Single-Stepping: Step into or over functions at a source or machine code level µCOS-II aware. One can enter into the Single-stepping mode after compiling the program successfully by pressing the key <F8>.

- Code disassembly: The disassembly window displays addresses, opcodes, and machine cycle times. Switch between debugging at machine-code level and source-code level by simply opening or closing the disassembly window.

- 4. Watch Expression: Watch expressions are compiled when defined, so complex expressions including function calls may be placed into watch expressions. Watch expressions can be updated with or without stopping program execution.

- 5. STDIO Window: printf outputs to this window and keyboard input on host PC can be detected for debugging purposes. Printf outputs may also be sent to serial port or file.

# 4.2 Disadvantages-

- ✓ More costly than other processors like ARM, Intel, etc.

- ✓ Less availability of Experts in the Rabbit market

# **4.3 Applications-**

- ✓ Serial-to-Ethernet applications

- ✓ Remote monitoring and communications

- ✓ Web-enabling devices

- ✓ Device/data management and control

Communication between Rabbit Processor & PC Using TCP

# <u>CHAPTER 5 -</u> <u>HARDWARE</u> <u>DESCRIPTION</u>

## 5.1 Rabbit 4000 Module-

The Rabbit 4000 has several powerful design features that practically eliminate EMI problems, which is essential for OEMs that need to pass CE and regulatory radiofrequency emissions tests. The amplitude of any electromagnetic radiation is reduced by the internal spectrum spreader, by gated clocks (which prevent unnecessary clocking of unused registers), and by separate power planes for the processor core and I/O pins (which reduce noise crosstalk). An auxiliary I/O bus can be used by designers to enable separate buses for I/O and memory or to limit loading the memory bus to reduce EMI and ground bounce problems when interfacing external peripherals to the processor. The auxiliary I/O bus accomplishes this by duplicating the Rabbit's data bus on Parallel Port A, and uses Parallel Port B to provide the processor's six or eight least significant address lines for interfacing with external peripherals.

Figure 12 Rabbit 4000 Module with 4300 Processor

The high-performance instruction set offers both greater efficiency and execution speed of compiler-generated C code. Instructions include numerous singlebyte opcodes that execute in two clock cycles, 16-bit and 32-bit loads and stores, 16bit and 32-bit logical and arithmetic operations,  $16 \times 16$  multiply (executes in 12 clocks), long jumps and returns for accessing a full 16 megabytes of memory, and onebyte prefixes to turn memory-access instructions into internal and external I/O instructions. Hardware-supported breakpoints ease debugging by trapping on code execution or data reads and writes.

Figure 13 Rabbit 4000 CPU Block Diagram

### **Development Kit comes complete with:**

- ✓ RCM4300 RabbitCore Module

- ✓ Prototyping Board

- ✓ Serial cable for programming and debugging

- ✓ Dynamic CÂ<sup>®</sup> integrated development software

- ✓ Getting Started Instructions

- Complete product documentation on CD including the Rabbit 4000 reference manual

- ✓ 240VAC adapter

- ✓ Rabbit 4000 pin specifications poster

Connectors and accessories

## 5.1.1 CLOCKS:

The Rabbit 4000 supports up to three separate clocks— the main clock, the 32 kHz clock, and the 20 MHz Ethernet clock.

*The Main Clock* is used to derive the processor clock and the peripheral clock inside the processor.

*The 32 KHz Clock* is used to drive the asynchronous serial bootstrap, the real-time clock, the periodic interrupt, and the watchdog timers. If these features are not used in a design, the use of the 32 kHz clock is optional.

*The Ethernet Clock* can be driven by the processor clock, the processor clock divided by 2, or by the input on PE6. The Ethernet clock needs to be 20 MHz to conform to the 10Base-T specification.

The Rabbit 4000 has a spectrum spreader on the main clock that shortens and lengthens clock cycles. This has the net effect of reducing the peak energy of clock harmonics by spreading the spectral energy into nearby frequencies, which reduces EMI and facilitates government-mandated EMI testing.

The *Various Registers* which are being used here are:

Global Control/Status Register (GCSR), Global Clock Modulator 0 Register (GCM0R), Global Clock Modulator 1 Register (GCM1R), Global Clock Double Register (GCDR), Global Output Control Register (GOCR), etc.

### 5.1.2 Rabbit System Management:

There are a number of basic system peripherals in the Rabbit 4000 processor. The peripherals which will be covered briefly in this part are the *periodic interrupt, the real-time clock, the watchdog timers, the battery-backed onchip-encryption RAM,* and some of the miscellaneous output pins and their control and processor registers that provide the processor ID and revision numbers.

The Periodic Interrupt, when enabled, is generated every 16 clocks of the 32 kHz clock (every 488  $\mu$ s, or 2.048 kHz). This interrupt can be used to perform periodic tasks.

The Real-Time Clock (RTC) consists of a 48-bit counter that is clocked by the 32 kHz clock. It is powered by the VBAT pin, and so can be batterybacked.

The Watchdog Timers are clocked by the 32 kHz clock. There are two Watchdog Timers in Rabbit 4000 Microprocessor Chip. The main watchdog timer can be set to time out from 250 ms to 2 seconds, while the secondary watchdog timer can time out from 30.5 µs up to 7.8 ms. The Main Watchdog Timer can reset the processor if not reload within the time, while the secondary watchdog timer generates a Priority 3 secondary watchdog interrupt when it is not reset within the time.

The battery-backed onchip-encryption RAM consists of 32 bytes of memory that are powered by the VBAT pin. Their values are not affected by reset, but are erased if the state of the SMODE pins changes.

## 5.1.3 Rabbit 4000 Specifications-

#### Communication between Rabbit Processor & PC Using TCP

| Packaging                 | 128-pin LQFP                                                | 128-ball TFBGA                   |  |

|---------------------------|-------------------------------------------------------------|----------------------------------|--|

| Package Size              | 16 x 16 x 1.5 mm                                            | 10 x 10 x 1.2 mm                 |  |

| Operating Voltage         | 1.8 V Core (3.3 V I/O                                       | ) or 1.8 V Core and I/O          |  |

| Ethernet                  | Integrated 10Base-T Ethemet controller                      |                                  |  |

| DMA                       | 8 independent channels with two external DMA request inputs |                                  |  |

| Operating Temp.           | -55°C to +85°C                                              |                                  |  |

| Maximum Clock Speed       | 60 MHz                                                      |                                  |  |

| Digital I/O               | 40+ (arranged in five 8-bit ports)                          |                                  |  |

| Serial Ports              | 6 CMOS-compatible                                           |                                  |  |

| Baud Rate                 | Clock speed/8 max asynchronous                              |                                  |  |

| Address Bus               | 24-bit                                                      |                                  |  |

| Data Bus                  | 8/1                                                         | 6-bit                            |  |

| Timers                    | Ten 8-bit, one 10-bit with two r                            | match registers, one 16-bit time |  |

| Real-Time Clock           | Yes, battery backable                                       |                                  |  |

| RTC Oscillator Circuitry  | External                                                    |                                  |  |

| Watchdog Timer/Supervisor | Y                                                           | ′es                              |  |

| Clock Modes               | 1x, 2x, /2, /3, /4, /6, /8                                  |                                  |  |

| Power Down Modes          |                                                             | (32 kHz)<br>(16, 8, 2 kHz)       |  |

| Auxiliary I/O Bus         | 8 data, 8 a                                                 | ddress lines                     |  |

#### Figure 14 Rabbit 4000 Specifications

## 5.1.4 Memory Management: