# PROGRAMMABLE WALSH PATTERN GENERATOR USING CPLD

А

Project Report

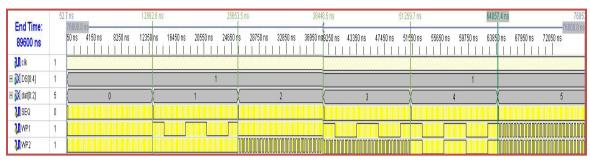

Submitted to

# GIANT METREWAVE RADIO TELESCOPE,

(National Centre for Radio Astrophysics), (Tata Institute of Fundamental Research)

Under the Guidance of

Mr. Ajith Kumar B.

Mr. Navnath D. Shinde

Engineer-E (GMRT-NCRA-TIFR)

&

Technical Assistant-C

2)

(GMRT-NCRA-TIFR)

Submitted by:

Meha Kainth B.TECH (ECE) (Jaypee University of Information Technology) Date:

# CERTIFICATE

This is to certify that *Ms. Meha Kainth*, a graduate student of B.Tech, Jaypee University of Information Technology, Solan (HP) has undertaken a project entitled *"Programmable Walsh Pattern Generator using CPLD"* at this institute from 15.06.2009 to 26.08.2009. She has done very good work and completed the project successfully.

# Ajith Kumar B.

Engineer – E GMRT –NCRA-TIFR Navnath D. Shinde Technical Assistant-C GMRT –NCRA-TIFR

# ACKNOWLEDGEMENTS

Working at Giant Meterwave Radio Telescope for student training program (STP) has been enriching experience for me. This project is result of many people's dedication, inspiration, guidance, knowledge and moral support. I would like to take this opportunity to thank them.

My foremost thanks to my guides, Mr. Ajith Kumar B. and Mr. Navnath D. Shinde, both of whom have helped me in every possible way in my project. It was really kind of them to devote their precious time and solve my difficulties. They were always eager to help me whenever I approached them, be it day or night. They not only cleared my concepts during this project, but also deepened my knowledge of the related topics.

I am highly grateful to the honorable Center Director of NCRA-GMRT, Mr. Rajaram Nityananda; Chief Scientist Mr. Yashwant Gupta; for giving me a chance to work in such a fabulous environment with all intellectuals around. I would like to express deep gratitude towards Mrs. N.S. Deshmukh, STP Coordinator, GMRT, for solving all my problems and offering me help to make my stay here more comfortable.

I feel delighted to express my sincere thanks to all the members of the Analog Lab, Ms. Sweta Gupta, Mr. Satpal Gole, Mr. Sudhir Phakatkar, Mr. R. Gosavi, Mr. Ramdas and Mr. Mangesh Bhor for providing me guidance and help through various stages of the project. I would also like to thank Srinivas for helping me with my project work and Aarti Sandikar for her cooperation.

Last but not the least; I am thankful to Mr. S. Sabhapathy for his support and sharing his beliefs and ideas with me and other STP students and for taking us all for the wonderful Shirdi trip and am also thankful to my friends Rolly Seth, Pritama Kundu, Abhijeet for their support.

Finally, I want to say thanks to all those who helped me directly or indirectly during this project and during my stay at GMRT Observatory.

Meha Kainth

# CONTENTS

| CERTIFICATE      | 1 |

|------------------|---|

| ACKNOWLEDGEMENTS | 2 |

| ABSTRACT         | 5 |

#

# CHAPTER 2-REPROGRAMMABLE SYSTEMS.....(16-22)

| 2.1. Reprogrammable Systems                     |  |

|-------------------------------------------------|--|

| 2.1.1. Types of Programmable Logic Devices/FPDs |  |

| 2.1.3. CPLD vs. EPROM                           |  |

# CHAPTER 3-DESIGN AND DEVELOPMENT......(23-45)

| 3.1. Walsh Functions                   |  |

|----------------------------------------|--|

| 3.1.1. Applications of Walsh Functions |  |

| 3.1.2. Definition and Properties                                 | 25 |

|------------------------------------------------------------------|----|

| 3.1.3. Generation of Walsh Patterns                              |    |

| 3.2. Selection of Walsh Patterns and Noise Patterns in D-49 PIU: |    |

| 3.2.1. Existing Design                                           |    |

| 3.2.2. New Design and Development                                |    |

# CHAPTER 4-PHYSICAL REALIZATION ON CPLD.....(46-59)

| 4.1 Physical Implementation on CPLD Chip |  |

|------------------------------------------|--|

| 4.1.1. Architecture of XC95108           |  |

| 4.1.2. Device Programming                |  |

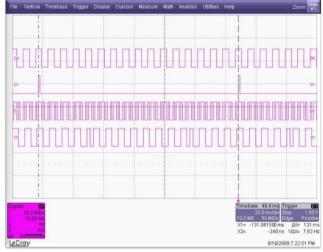

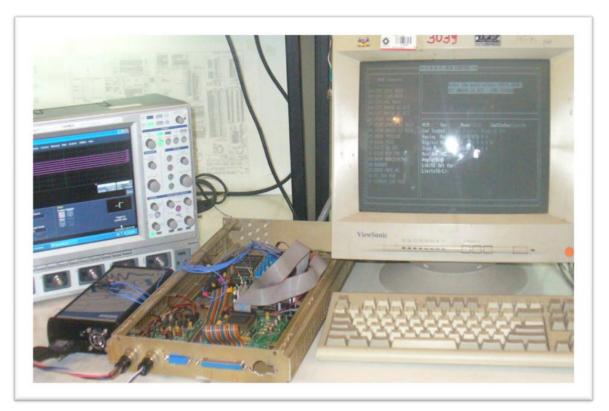

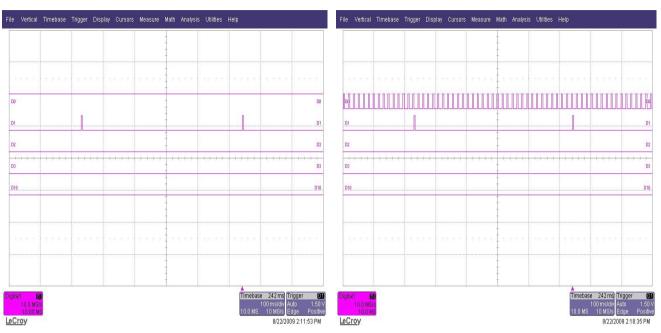

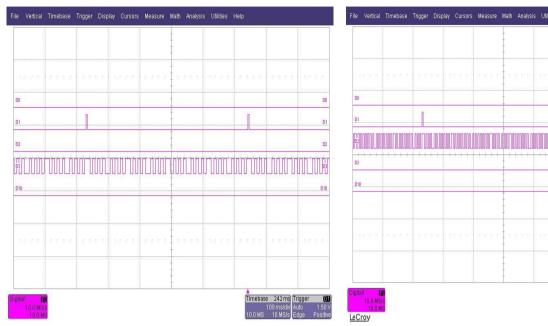

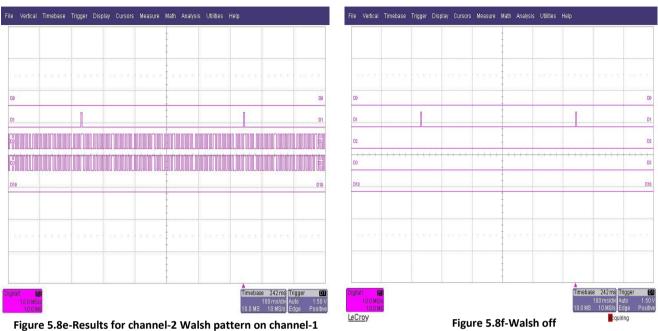

| 4.2. Results on MSO                      |  |

# CHAPTER 5-HARDWARE IMPLEMENTATION AND TESTING......(60-72)

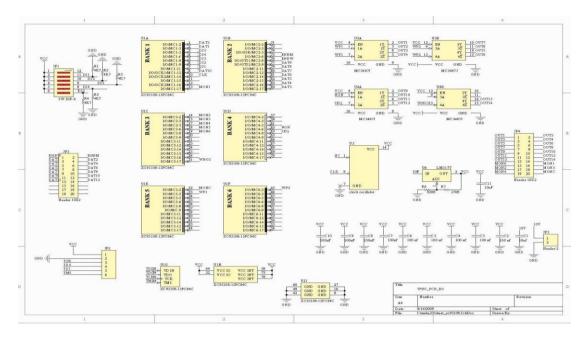

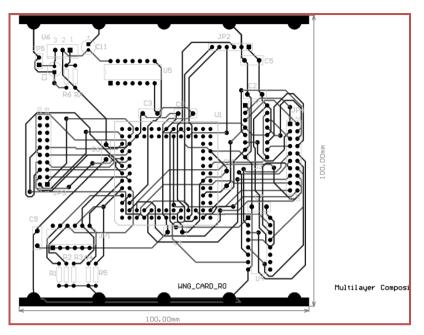

| 5.1. Walsh Card PCB Design      | 61 |

|---------------------------------|----|

| 5.2. Testing the Walsh Card PCB | 62 |

| 5.2.1. Test Setup               | 63 |

| 5.2.2. Procedure for Testing    | 64 |

| 5.3. Test Results               | 67 |

#

| 6.1. C | clusions74 |

|--------|------------|

|        |            |

| FUTURE SCOPES |    |

|---------------|----|

| REFERENCES    | 76 |

| APPENDIX A    | 77 |

| APPENDIX B    |    |

| APPENDIX C    |    |

# ABSTRACT

The VLSI technology has made revolutionary changes in status of electronic industry and capturing the digital design by schematic entry, hardware description or combination of both. With the recent advancements in Field Programmable Gate Arrays (FPGA) and Complex Programmable Devices (CPLD), it has been possible to design a system on a programmable chip (SOC).

A circuit to control certain Front-end System parameters, through MCM-2 (in the LO Synthesiser) in the GMRT receiver chain is developed. This report describes in detail the circuit design and implementation. An introduction to Walsh functions is given and an efficient method of Walsh pattern generation has been described. The logic for Walsh pattern generation forms the main part of the front end control circuit along with various other logics for noise pattern generation, sequency pattern generation and control of monitoring signals. The overall architecture for various patterns generation has been programmed in a CPLD using Xilinx Design Tools 8.2i, so as to develop a SOC. Additional functional features have been added to this circuit to provide more flexibility to a user while observation. Finally, the overall circuit has been implemented on a PCB using Altium Design Tools 6.1and the final PCB has been tested online. The various results obtained after testing have been compared with the calculated and the simulated results.

# CHAPTER-I

# INTRODUCTION

ARRA

National Centre for Radio Astrophysics TATA INSTITUTE OF FUNDAMENTAL RESEARCH

# **1.1. INTRODUCING GMRT**

Giant Metrewave Radio Telescope (GMRT), located near Pune in India, is the world's largest radio telescope working at metre wavelengths. It is operated by the National Centre for Radio Astrophysics, a part of the Tata Institute of Fundamental Research, Mumbai. In the form of GMRT, NCRA (National Center for Radio Astrophysics, TIFR) has set up a unique facility for radio astronomical research using the metre wavelengths range of the radio spectrum.

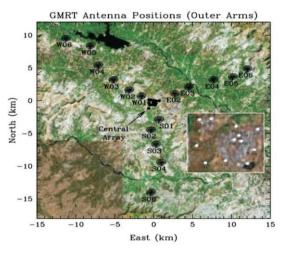

Giant Metrewave Radio Telescope (GMRT) is located at a site about 80 KM north of Pune. It is an aperture synthesis array consisting of 30 fully steerable giant parabolic dishes of 45m diameter. GMRT is one of the most challenging experimental programmes in basic sciences undertaken by Indian scientists and engineers.

GMRT, about 10 km east of Narayangaon town on the Pune-Nasik highway, was selected after an extensive search in many parts of India, considering several important criteria such as low man-made radio noise, availability of good communication, vicinity of industrial, educational and other infrastructure and, a geographical latitude sufficiently north of the geomagnetic equator in order to have a reasonably quiet ionosphere and yet be able to observe a good part of the southern sky as well.

# 1.1.1. Why Metre Wavelengths?

The study of universe at high frequencies can easily be done, but the most challenging work was to develop a telescope which can work at low frequencies or more specifically Radio Frequencies because this is the range of frequencies in which maximum noise lies. Since in other countries like USA, the RF Noise level is too high, no other country had taken an initiative to develop such a system working at this frequency range. The RF noise level being comparatively low in India, gave an opportunity to pick up this challenging project of GMRT working at Radio frequencies. Hence, the metre wavelength part of the radio spectrum has been particularly chosen for study with GMRT because man-made radio interference is considerably lower in this part of the spectrum in India. Although there are many outstanding astrophysics problems which are best studied at metre wavelengths, there has, so far, been no large facility anywhere in the world to exploit this part of the spectrum for astrophysical research.

GMRT currently operates at five observing bands centered at 150 MHz, 235 MHz, 327 MHz, 610 MHz and an L-band extending from 1000 to 1450 MHz. The Astronomical bodies that can be best studied at metre wavelengths through GMRT are – Pulsars, Sun, Jupiter Radio Bursts, Hydrogen Lines, Milky way and other nearby Galaxies.

# 1.1.2. Array Configuration

The number and configuration of the dishes was optimized to meet the principal astrophysical objectives which require sensitivity at high angular resolution as well as ability to image radio emission from diffuse extended regions. The GMRT has a hybrid configuration, with 14 of its antennas randomly distributed in a central region ( $\sim 1$  km across), called the central square. The distribution of antennas in the central square was deliberately "randomized" to avoid grating lobes.

Figure 1.1-The GMRT array as viewed from space.

Figure 1.2-One of the 30 GMRT antennae

The remaining antennas are distributed in a roughly Y shaped configuration, with the length of each arm 1 of the Y being ~14 km. The maximum baseline length between the extreme arm antennas is ~25 km. The arms are called the "East", "West" and "South" arms. The central square antennas provide a large number of relatively short baselines. This is very useful for imaging large extended sources, whose visibilities are concentrated near the origin of the UV plane. The arm antennas on the other hand are useful in imaging small sources, where high angular resolution is essential. A single GMRT observation hence yields information on a variety of angular scales

GMRT is an indigenous project. The construction of 30 large dishes at a relatively small cost has been possible due to an important technological breakthrough achieved by Indian Scientists and Engineers in the design of light-weight, low-cost dishes. The design is based on what is being called the **`SMART'** concept - for **S**tretch **M**esh **A**ttached to **R**ope **T**russes.

### 1.1.3. GMRT front-ends and back-ends

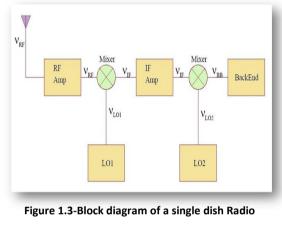

Radio waves from the distant cosmic source impinge on the antenna and create a fluctuating voltage at the antenna terminals. This voltage varies at the same frequency as the cosmic electro-magnetic wave, referred to as the *Radio Frequency (RF)*. The voltage is first amplified by the front-end (or Radio Frequency) amplifier. The signal is weakest here, and hence it is very important that the amplifier introduce as little noise as possible.

Telescope

Front end amplifiers hence usually use low noise solid state devices. After amplification, the signal is passed into a *mixer*. A mixer is a device that changes the frequency of the input signal. Mixers have two inputs, one for the signal whose frequency is to be changed (the RF signal in this case), and the other input is usually a pure sine wave generated by a tunable signal generator, the *Local Oscillator (LO)*. The output of the mixer is at the beat frequency of the radio frequency and the local oscillator frequency. So after mixing, the signal is now at a different (and usually lower) frequency than the RF, this frequency is called the *Intermediate Frequency (IF)*. The main reason for mixing (also called heterodyning) is that though most radio telescopes operate at a wide range of radio frequencies, the processing required at each of these frequencies is identical. The economical solution is to convert each of these incoming radio frequencies that the telescope accepts. In telescopes that use co-axial cables to transport the signal across long distances, the IF frequency is also usually chosen so as to minimize transmission loss in the cable. Sometimes there

is more than one mixer along the signal path, creating a series of IF frequencies, one of which is optimum for signal transport, another which is optimum for amplification etc. This is called a *'super-heterodyne'* system. After conversion to IF, the signal is once again amplified (by the IF amplifier), and then mixed to a frequency range near 0 Hz (*the Base Band (BB)*) and then fed into the *backend* for further specialized processing. What backend is used depends on the nature of the observations.

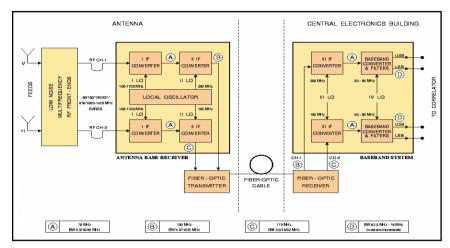

The GMRT accepts radio waves in six bands from 50 MHz to 1.4 GHz and has IFs at 130 MHz, 175 MHz and 70 MHz. The GMRT receiver chain is shown schematically in Figure 1.4.

- The first block is the multi-frequency front-end. This is located in a rotating turret at the prime focus. All the feeds and low noise RF front-ends have been configured to receive dual polarization signals. Lower frequency bands (from 50 to 610 MHz) have dual circular polarization channels, i.e. left circular and right circular polarizations which have been labeled as CH1 and CH2 respectively. The L-band (1000-1450 MHz) system has dual linear polarization channels, i.e. vertical and horizontal polarizations (also labeled CH1 and CH2 respectively).

- The first local oscillator (I LO, situated at the base of the antenna, inside a shielded room) converts the RF band to an IF band centered at 70 MHz. After passing the signal through a bandpass filter of selectable bandwidth, the IF at 70 MHz is then translated (using II LO) to a second IF at 130 MHz and 175 MHz for CH1 and CH2, respectively. The maximum bandwidth available at this stage is 32 MHz for each channel.

- This frequency translation is done so that signals for both polarizations can be frequency division multiplexed onto the same fiber for transmission to the Central Electronics Building (CEB). The IF signal at 130 MHz and 175 MHz along with telemetry and LO round trip phase carriers directly modulate a laser diode operating at 1300nm antennas and the CEB.

- At the CEB, these signals are received at 'nm' wavelengths which are coupled to a single mode fiber-optic link by the Fiber-Optic Receiver and the 130 and 175 MHz signals are then separated out and sent for base band conversion. The baseband converter section converts the 130 and 175 MHz IF signals first to 70 MHz IF (using III LO), these are

then converted to upper and lower sidebands (each at most 16 MHz wide) at 0 MHz using a tunable IV LO. There are also two Automatic Level Controllers (ALCs) in the receiver chain.

1.4- Schematic Diagram of GMRT Receiver chain

- There are a variety of digital backends available at the GMRT. The principal backend used for interferometric observations is a 32 MHz wide FX correlator. The FX correlator produces a maximum of 256 spectral channels for each of two polarizations for each baseline.

- All control and monitoring commands to the system are sent from the central computer through a telemetry system. The telemetry system provides a Measurement, Control and Monitor (MCM) circuit for sending digital control data to the circuits and for acquiring analog monitor data.

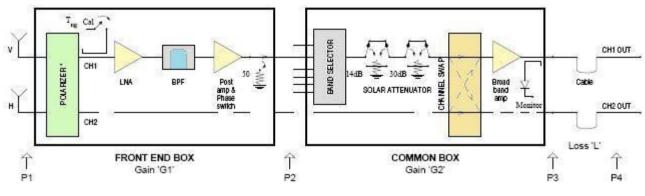

## **1.2. EXISTING FRONT- END ELECTRONICS**

★ At the focus of each antenna, each feed has two low noise amplifiers (one for each polarization), with a noise injection facility where the user can select any of the 4 values of injected noise power. The two signals go to a common box (also on the feed turret) where the user can select which frequency signals appear at the output of the common box since only 2 cables go down to the antenna base. The common box has facilities for the user to select solar attenuators (0, 14, 30 or 44 dB) and swap the two polarization channels.

There is a bandpass filter after the LNA in the front end box, which is followed by a post amplifier, to have the required output power at the end of front end box. Thereafter the signal is modulated with Walsh function using phase switching to minimize the effect of crosstalk between different signals. Mini-circuits double balanced mixer SBL-1MH is used for phase-switching.

2.5- Schematic Diagram of GMRT Front End System

★ At the correlator the exact reverse phase switching is done for each antenna so that the original phase is recovered just before the cross correlation is done. Such a scheme can greatly reduce the cross-talk at all points between the RF amplifier and the baseband.

# 1.3. FRONT-END CONTROL FROM LO SYNTHESISER

All the front end parameters are controlled through a MCM-5 in the front end. Few of the parameters of the front end system are varied at the time of observation of a celestial source. All these front end parameters along with switching ON/OFF of the front end MCM are controlled at the Antenna Base Rack in the Local Oscillator Synthesiser. Before analyzing the requirements for the front end control of the GMRT, it is necessary to understand what is noise calibration and Walsh switching and why are these required for the GMRT.

# 1.3.1. Noise Calibration

An additional noise signal (of known strength) is injected (as described above) into the RF signal to measure the system temperature. The noise generator at the front-end of each antenna can be switched in both power and Time Domains for different durations as per the requirement. The advantages of noise injection facility are as follows:

- This facility is used in order to calibrate the gain of the receiver. By adding noise of known strength, SNR is decreased be a known amount and the variation in gain of the system can be measured. For example, the front end noise generator is to be kept on continuously for duration in order to troubleshooting the receiver system. This is however, not used for online observation purposes.

- It may be used a secondary calibration system, the primary being the standard celestial sources. By synchronously measuring the total power, it is possible to calibrate the system temperature.

The synchronous total power measurement however has not yet been implemented.

# 1.3.2. Walsh Switching

Signals from one antenna could leak into another antenna at various points along the signal flow chain. This is normally referred to as *cross-talk*. This would cause a spurious correlation between the baseband signals from these two antennas. This leakage can be minimized by switching the phase of the RF signal of each antenna by a pattern that is ortho-normal to the pattern used for all other antennas. Typically the ortho-normal functions used are Walsh functions, and this scheme is called *Walsh Switching*.

# 1.3.3. Requirements for the Front End System from the LO Synthesiser:

- > Generation and selection of noise patterns for noise switching.

- > Generation and selection of Walsh patterns for Walsh switching at the front end.

- Switching ON and OFF the front end MCM.

## Switching of Front-end Noise Generator in Time Domain:

The Noise switching in power domain is achieved by switching appropriate attenuators and the switching in time domain by a switching pattern in time, which is produced at base of the antenna in the Antenna Base Rack (ABR) and will be described later. It is possible to inject noise at any one of four levels. Four patterns are available, NGN1, NGN2, NGN3, NGN4 corresponding to 0%, 25%, 50%, and 100% ON period for the noise generator. The noise at any antenna can be switched on and off (on sub second time scales) according to a pre-determined pattern, which is encoded in PROMs in the Antenna Based Receiver (ABR).

#### Walsh switching at the front end:

A phase switching facility using separate Walsh functions for each signal path is available at the RF section of the receiver. As discussed previously, a set of Walsh patterns are produced at the base of each antenna, for the following two purposes:

- To phase-modulate the RF output of the LNA in the front-end using a double balanced mixer as a broad band phase switch. This is to take care of coupling between the two signal channels of an antenna as well as coupling of signal between antennas. The demodulation will be done at an appropriate location in the correlator.

- To phase-modulate the return LO referance signal. As phase-coherent LO reference signals at 105 Mhz are received at CEB through the return link from all thirty antennas, it is felt that there might be coupling between signals at CEB to result in inaccuracies of RTP measurement. Hence phase switching of the LO return signal might be essential. However, this scheme has not been implemented as yet.

128 Walsh patterns with 128 transitions over a period of the function, defined as sequency, have been generated using a program. The sequency pattern uniquely defines the start of Walsh pattern. So, there are 64 pairs of Walsh patterns for use in 30 antennas (for each of the two channels of every antenna) divided into 'Low Group' and 'High Group'. The first and the last patterns are not used. The required Walsh patterns for each antenna are also encoded in PROMs situated at the ABR.

#### Switching ON and OFF the Front end MCM

MCM-5 is placed in the front end and is to be switched off at the time of observation. This is done because an MCM consist of microprocessor, digital circuitry which generates a lot of RFI (Radio Frequency Interference) and since this MCM is in the front end, near the feeds, the feeds can pick up the RFI and thus resulting in undesirable results. Again the required signal for controlling the MCM ON/OFF is controlled at the ABR.

### 1.3.4. Control at the ABR

The Monitor and Control Module-2 (MCM-2) in the control digital Plug-In-Unit, D-49 PIU which is placed at the ABR in the LO Synthesiser, controls the selection of various patterns at the ABR which will be combined with the RF signals at the front-end and the control of front end MCM, as per the online commands issued by the user in the control room. A Walsh card

PCB WNG\_RO in the PIU is used for this purpose and consists of EPROM which is encoded with the various patterns this PCB also generates the various monitoring signals for enabling the Monitoring card PCB in the D-49 PIU. The complete process of pattern selection has been discussed later. An interface panel with a 10-way terminal strip has been provided at the rear of the ABR rack to bring the patterns from rear of D-49 PIU to a convenient location for connecting to the 10-core front-end cable.

# **1.4. PROBLEM DEFINITION**

The main aim of the project is to make Front End control to control Front End system parameters through MCM-2 in the ABR. This involves improving the Walsh card PCB in the D-49 PIU. This PCB consists of digital circuitry having a number of IC's with differential line driver circuitry for long distance transmission of signals from the antenna base to the front end. All this Digital circuitry part can be simulated in the CPLD and thus saving the cost and providing better performance in comparison to the EPROM based circuitry of the existing Walsh card. Hence, the new Walsh card consists of the CPLD and differential line driver circuitry with minimum Components and thus size. Besides reducing the size, additional functionality can be added to the card by programming the CPLD in order to improve the overall performance and provide more flexibility to the user for better analysis while observation.

### Overview of the work that has to be done:

- > Understanding the working and function of the Walsh Card PCB.

- > Understanding the Walsh functions and finding the most efficient method for generation of Walsh Patterns for the GMRT.

- Developing the logic for Walsh pattern generation, Sequency pattern generation, noise pattern generation, front end MCM control and Monitoring signals control.

- Selection of a suitable CPLD.

- > Physical realization of the various logics in the CPLD.

- > Preparing a PCB with this CPLD and other circuitry for implementing the complete functionality of the Walsh card PCB.

- > Testing the PCB online.

# 2.1. REPROGRAMMABLE SYSTEMS

Reconfigurable Computing has been described as hardware going soft. A computing platform based on this principle has an architecture that can be modified by the software to suit the application at hand. An algorithm will always run fastest when directly hardwired (DSP, ASIC). Dramatic performance gains can therefore be obtained by implementing an algorithm in the reconfigurable portion of such a system. Prompted by the development of new types of sophisticated field-programmable devices (FPDs), the process of designing digital hardware has changed dramatically over the past few years. Unlike previous generations of technology, in which board-level designs included large numbers of SSI chips containing basic gates, virtually every digital design produced today consists mostly of high-density devices. This applies not only to custom devices like processors and memory, but also for logic circuits such as state machine controllers, counters, registers, and decoders. When such circuits are destined for high-volume systems they have been integrated into high-density gate arrays. The most compelling advantages of FPDs are instant manufacturing turnaround, low start-up costs, low financial risk and (since programming is done by the end user) ease of design changes.

The market for FPDs has grown dramatically over the past decade to the point where there is now a wide assortment of devices to choose from. A designer today faces a daunting task to research the different types of chips, understand what they can best be used for, choose a particular manufacturer's product, learn the intricacies of vendor-specific software and then design the hardware. Confusion for designers is exacerbated by not only the sheer number of FPDs available, but also by the complexity of the more sophisticated devices.

*Field-Programmable Device (FPD)* is a general term that refers to any type of integrated circuit used for implementing digital hardware, where the chip can be configured by the end user to realize different designs. Programming of such a device often involves placing the chip into a special programming unit, but some chips can also be configured "in-system". Another name for FPDs is *programmable logic devices* (PLDs).

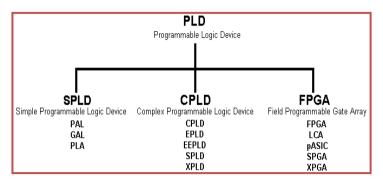

# 2.1.1. Types of Programmable Logic Devices/FPDs

Many types of programmable logic are available. The current range of offerings includes everything from small devices capable of implementing only a handful of logic equations to huge CPLDs that can hold an entire processor core (plus peripherals). In addition to this incredible difference in size there is also much variation in architecture. Some of the most common types of programmable logic devices have been mentioned as under:

Figure 2.1- Hierarchy of various PLDs

## **PLDs**

At the low end of the spectrum are the original Programmable Logic Devices (PLDs). These were the first chips that could be used to implement a flexible digital logic design in hardware. In other words, you could remove a couple of the 7400-series TTL parts (ANDs, ORs, and NOTs) from your board and replace them with a single PLD. Other names for this class of device are Programmable Logic Array (PLA), Programmable Array Logic (PAL), and Generic Array Logic (GAL).

PLDs are often used for address decoding, where they have several clear advantages over the 7400-series TTL parts that they replaced. First, of course, is that one chip requires less board area, power, and wiring than several do. Another advantage is that the design inside the chip is flexible, so a change in the logic doesn't require any rewiring of the board. Rather, the decoding logic can be altered by simply replacing that one PLD with another part that has been programmed with the new design.

Inside each PLD is a set of fully connected macrocells. These macrocells are typically comprised of some amount of combinatorial logic (AND and OR gates, for example) and a flip-flop. In other words, a small Boolean logic equation can be built within each macrocell. This equation will combine the state of some number of binary inputs into a binary output and, if necessary, store that output in the flip-flop until the next clock edge. Of course, the particulars of the available logic gates and flip-flops are specific to each manufacturer and product family. But the general idea is always the same.

## **CPLDs**

As chip densities increased, it was natural for the PLD manufacturers to evolve their products into larger (logically, but not necessarily physically) parts called *Complex Programmable Logic*  Devices (CPLDs). For most practical purposes, CPLDs can be thought of as multiple PLDs (plus some programmable interconnect) in a single chip. The larger size of a CPLD allows the implementation of either more logic equations or a more complicated design. In fact, these chips are large enough to replace dozens of 7400-series parts. When a CPLD is configured, the internal circuitry is connected in a way that creates a hardware implementation of the software application. Unlike processors, CPLDs use dedicated hardware for processing logic and do not have an operating system. CPLDs are truly parallel in nature so different processing operations do not have to compete for the same resources. As a result, the performance of one part of the application is not affected when additional processing is added. Also, multiple control loops can run on a single CPLD device at different rates. CPLD-based control systems can enforce critical interlock logic and can be designed to prevent I/O forcing by an operator. However, unlike hard-wired printed circuit board (PCB) designs which have fixed hardware resources, CPLD-based systems can literally rewire their

internal circuitry to allow reconfiguration after the control system is deployed to the field.

CPLDs store their logic design in an EPROM, EEPROM, flash or SRAM memory that associates each programmable connection point with a memory cell (is the connection open or closed). The building block of a CPLD is the macro cell, which contains logic implementing disjunctive normal form expressions and

more specialized logic operations. CPLD- Produced by Altera, AMD, Lattice, Xilinx and etc

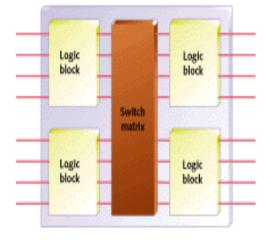

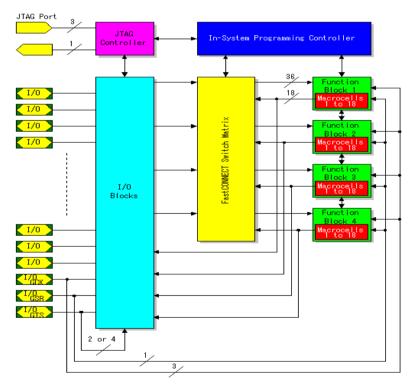

Figure 2.2- Internal structure of a CPLD

#### 2.1.2. Architecture of CPLD

As shown in above figure, there are logic blocks which are themselves comprised of macrocells and interconnect wiring, just like an ordinary PLD. The macrocells within a function block are usually fully connected. If a device contains multiple function blocks, then the function blocks are further interconnected. In concept, CPLDs consist of multiple PAL-like logic blocks interconnected together via a programmable switch matrix. Typically, each logic block contains 4 to 16 macrocells, depending on the architecture.

Figure 2.3- Arrangement of Macro Cells within a logic block

Some of the major variations between CPLD architectures include the number of product terms per macrocell, whether product terms from one macrocell can be borrowed or allocated to another macrocell, and whether the interconnect switch matrix is fully- or partially-populated. In some architectures, when the number of product terms required exceeds the number available in the macrocell, additional product terms are borrowed from an adjoining macrocell. This makes the CPLD device useful for a wider variety of applications.

When borrowing product terms from an adjoining macrocell, that macrocell may no longer be useful. In some architectures, the macrocell still has some basic functionality. Borrowed product terms usually mean increased propagation delay.

Another difference in architectures is the number of connections within the switch matrix. A switch matrix supporting all possible connections is fully populated. A partially- populated switch supports most, but not all, connections. The number of connections within the switch matrix determines how easy a design will fit in a given device. With a fully-populated switch matrix, a design will route even with a majority of the device resources used and with fixed I/O pin assignment. Generally, the delays within a fully populated switch matrix are fixed and predictable. At the high-end (in terms of numbers of gates), there is also a lot of overlap in potential applications with CPLDs. Because of its less flexible internal architecture, the delay through a CPLD (measured in nanoseconds) is more predictable and usually shorter. In short, we can conclude the following points about CPLDs:

#### • Significant characteristics for the CPLD-architecture:

- » product terms generated in programmable macrocells.

- » typically one dedicated flip-flop per macrocell.

- » many macrocells per logic-block.

- » typically all logic-blocks identical.

- » minimum two logic-blocks per device.

- » routing between logic-blocks via global switch matrix.

#### • Main-advantages :

- » predictable timing

- » fast pin-to-pin delay

- » efficient resource utilization by switch-matrix

- » medium design complexities possible

#### Programming a CPLD

In order to program a CPLD, solder the device to its printed circuit board, and then feed it with a serial data stream from a personal computer. The CPLD is in-circuit programmable and contains a circuit that decodes the data stream and configures the CPLD to perform its specified logic function via a JTAG interface or from an on-board embedded processor. This makes it possible to erase and reprogram the device internals.

#### FPGAs

FPGAs use a grid of logic gates, similar to that of an ordinary gate array, but the programming is done by the customer, not by the manufacturer. The term "field-programmable" means the array is done outside the factory, or "in the field." FPGAs are usually programmed after being soldered down to the circuit board, in a manner similar to that of larger CPLDs. In most larger FPGAs the configuration is volatile, and must be re-loaded into the device whenever power is applied or different functionality is required.

The main difference between FPGAs and CPLDs is that FPGAs have a volatile memory, thus it requires to be programmed after power up. CPLDs do not. Also, FPGAs usually consume more power than CPLDs due to their SRAM nature. Finally, CPLDs do not have as many registers or memory storage as FPGAs. In general CPLDs are a good choice for wide combinatorial logic applications while FPGAs are more suitable for large state machines (i.e. microprocessors). FPGAs are internally based on Look-up tables (LUTs) while CPLDs form the logic functions with sea-of-gates (e.g. sum of products).

#### 2.1.3. CPLD vs. EPROM

Before PLDs were invented, read-only memory (ROM) chips were used to create arbitrary combinational logic functions of a number of inputs. Consider a ROM with m inputs (the address lines) and n outputs (the data lines). When used as a memory, the ROM contains  $2^m$  words of n bits each. Now imagine that the inputs are driven not by an m-bit address, but by m independent

logic signals. Theoretically, there are  $2^m$  possible Boolean functions of these *m* signals, but the structure of the ROM allows just  $2^n$  of these functions to be produced at the output pins. The ROM therefore becomes equivalent to *n* separate logic circuits, each of which generates a chosen function of the *m* inputs.

The advantage of using a ROM in this way is that any conceivable function of the *m* inputs can be made to appear at any of the *n* outputs, making this the most general-purpose combinatorial logic device available. Also, PROMs (programmable ROMs), EPROMs (ultraviolet-erasable PROMs) and EEPROMs (electrically erasable PROMs) are available that can be programmed using a standard PROM programmer without requiring specialized hardware or software. However, there are several disadvantages:

- They are usually much slower than dedicated logic circuits,

- They cannot necessarily provide safe "covers" for asynchronous logic transitions so the PROM's outputs may glitch as the inputs switch,

- They consume more power, and

- Because only a small fraction of their capacity is used in any one application, they often make an inefficient use of space.

- PROM and EPROM can only be encoded with the help of a separate piece of lab equipment called a device programmer. On the other hand, CPLDs based on EEPROM or Flash technology are in-circuit programmable. In other words, the additional circuitry that's required to perform device (re)programming is provided within the FPGA or CPLD silicon as well. This makes it possible to erase and reprogram the device internals via a JTAG interface or from an on-board embedded processor.

# CHAPTER-III DESIGN AND DEVELOPMENT

# **3.1. WALSH FUNCTIONS**

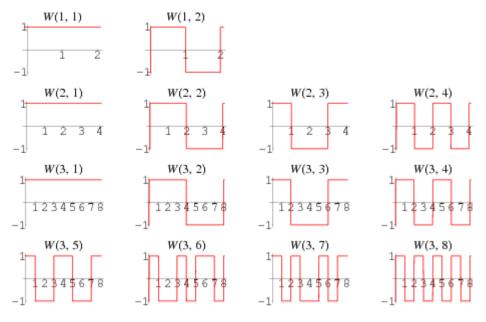

Figure 3.1-walsh patterns

Walsh functions are a series of square waves that can be combined to create almost any waveform. These functions consist of trains of square pulses (with the allowed states being -1 and 1) such that transitions may only occur at fixed intervals of a unit time step; the initial state is always +1. The function WAL(i,k) represents a waveform, known as *Walsh Pattren*, as a function of time k with i transitions over the period of the function defined as *Sequency function*. Thus, the parameter n can be interpreted as "one half the number of zero crossings per unit time. i is known as the normalized sequency or sequency. For an index n,  $i=log_2n$ . There are  $2^n$  Walsh functions of length  $2^n$ . Furthermore, within the set of  $2^n$  functions there is one function of zero sequency, one of (normalized) sequency  $2^{n-1}$ , and one pair (odd and even) of each (normalized) sequency from 1 to  $2^{n-1} - 1$ . The Walsh functions are commonly subdivided into the even functions Cal(i,k), and the odd functions Sal(i,k) which are defined by:

$$Cal(i,k) = wal(2i,k)$$

$$Sal(i,k) = wal(2i-1,k)$$

#### 3.1.1. Applications of Walsh Functions

Walsh functions and transforms are important analytical tools for signal processing and have wide applications in digital communication, digital image processing, statistical analysis, solving differential equations as well as in digital logic design. The Walsh function series can be applied to many areas where sinusoidal techniques have previously dominated. This is so in the design of digital equipment for communication and computer applications, where the two levels that form the function match binary logic. In the applications of the Walsh transform to CDMA, VLSI testing, cryptography, and digital signal and image processing, the fastest approach is the hardware implementation.

#### Applications of Walsh functions in Radio Astronomy Instruments

An effective means of getting a further reduction of several tens of decibels in the unwanted responses is known as phase switching. In case of phase switching, the RF signal received at one of the antennas is periodically reversed in phase by a switch that is driven by a square wave a few tens of Hertz. The component of the multiplier outputs resulting from the signals entering the antennas reverses in sign following the action of the switch, and is rectified by synchronous detectors. The unwanted signals, which are not phase switched, produce components which are essentially constant at the multiplier outputs and thus are eliminated by the synchronous detection.

For phase switching a multielement array in which the products of the signals from all possible pairs of antennas are to be formed, phase switching can be represented by multiplication of the received signals by periodic functions that alternate in time between values of +1and -1. For the  $m_{th}$  and  $n_{th}$  antennas let these functions be  $f_m(t)$  and  $f_n(t)$ . Synchronous detection of the multiplier output for these two antennas requires a reference waveform  $f_m(t)f_n(t)$ , and any nonvarying components from the multiplier are reduced by a factor

$$\frac{1}{T}\int_{0}^{T}f_{\rm m}(t)f_{\rm n}(t)$$

after averaging for a time T. This factor will be zero if  $f_m(t)$  and  $f_n(t)$  are orthogonal over the interval T or a submultiple of it.

## 3.1.2. Definition and Properties

Many different definitions for Walsh functions are known and used for various applications. These functions are commonly defined in terms of a subset, the Rademacher functions.

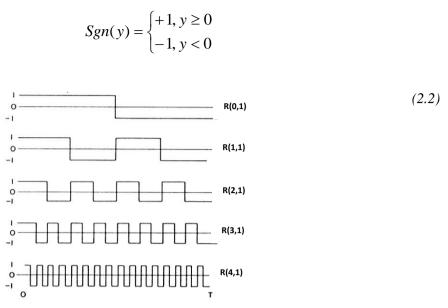

• A Rademacher function of the nth order is defined as:

$$R_m(k) = Sgn(\sin 2\pi 2^m k), \quad m = 0, 1, 2...$$

(2.1)

Where, the signum function Sgn(y) is defined by:

Figure 3.2- Rademacher-functions R<sub>0</sub> to R<sub>4</sub>

## Property 3.1:

Rademacher functions form an orthogonal, but incomplete set. Actually, they form a subset of the Walsh set of functions. The Rademacher functions  $R_m(k)$  are the walsh functions of index  $2^m-1$

$$R_{\circ}(k) = wal (2^{\circ} - 1, k) = sgn (sin 2\pi k)$$

$$R_{\circ}(k) = wal (2^{\circ} - 1, k) = sgn (sin 4\pi k)$$

And in general,

$$R_m(k) = wal \left(2^{m+1} - 1, k\right) = sgn\left(\sin 2^{m+1}\pi k\right), \ k \ge 0.$$

(2.3)

First Walsh pattern i.e. w(0,k) is a series of all 1's and 0 sequency.

### Property 3.2:

The product of any two Walsh functions is a third Walsh function

$$wal(i, k) . wal(j, k) = wal(p, k)$$

(2.4)

such that

$$\langle i \oplus j \rangle = \langle p \rangle \tag{2.5}$$

Where (.) means that if i, j, p are expressed as binary numbers, then p is formed from the bit-bybit modulo-2 sum of i and j. Equation (2.3) may be written alternatively as

$$\langle i \oplus j \oplus p \rangle = \langle 0 \rangle$$

For convenience and simplicity of notation the Walsh functions can be considered to be formed from (0, 1) values rather than from (+ 1, - 1) values; multiplication of the functions is then replaced by modulo-2 addition, the (0, 1) values  $x_i$  being related to the (+1, -1) values  $y_i$  by the equation

$$y_i = 1 - 2x_i$$

wal(i, k) will for briefness be written w(i) and  $R_m(k)$  will be written  $R_m$ .

## Property 3.3:

An arbitrary Walsh function w(i) may be written as a linear combination of Walsh functions all with index of the form  $2^m$ . For if the binary equivalent of *i* is  $b_z b_{z-1} \dots b_3 b_2 b_1 b_0$ , (with  $b_0$  as the least significant digit) then

$$i = (b_0 2^0 \oplus b_1 2^1 \oplus b_2 2^2 \oplus \dots)$$

$$= \sum_{m=0}^{z} b_m 2^m$$

(2.6)

where the summation symbol denotes the modulo-2 sum. Therefore,

$$w(i) = \sum_{m=0}^{z} b_m w(2^m), \qquad b_m \in \{0,1\}$$

(2.7)

This is evident from (2.4) and (2.5) and shows that an arbitrary Walsh function w(i) may be written as a linear combination of Walsh functions with indices of the form  $2^m$ , and that the combination required is obtained directly from the binary equivalent of *i*.

For example, if i = 50 (= 110010 in binary)

$$w(50) = w(2^5) \oplus w(2^4) \oplus w(2^1)$$

$$= w(32) \oplus w(16) \oplus w(2)$$

$$= w(32) \oplus w(13)$$

## Property 3.4:

Any Walsh function may also be expressed as a linear combination of the Rademacher functions:

$$w(i) = \sum_{m=0}^{z} g_m w (2^{m+1} - 1) = \sum_{m=0}^{z} g_m R_m, \quad g_m \in \{0, 1\}$$

(2.8)

The  $g_m$  forms the Gray code equivalent of *i*.

### 3.1.3. Generation of Walsh Patterns

Many different definitions for Walsh functions are known and used for various applications. They include: Walsh functions in strict sequency ordering (known also as Walsh - Kaczmarz) related to Sal and Cal symmetries; Walsh functions in dyadic Paley ordering (known also as Dyadic) known also as Gray code ordered functions; Walsh functions in natural Hadamard ordering; Walsh functions in X-ordering; and Walsh functions in reverse Gray ordering. Since they are square waves, they are very easy to create. Various Walsh function generators exist that use different methods. The sequence generators having the widest applicability are those generating a set of Walsh functions, although in some cases these functions are obtained by first generating Rademacher functions. Ideally, the generated functions should be orthogonal to each other and some designs are better in achieving this than others. For the second case, the Walsh orderings form a group under modulo-2 addition and such generators can be easily implemented using multiplicative EXOR gates.

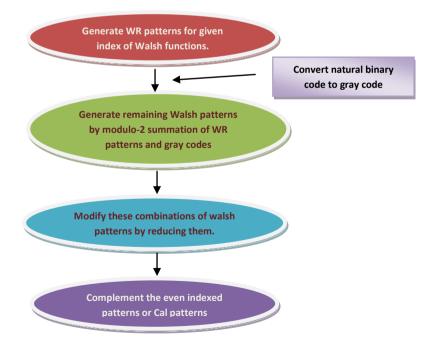

For our project, we have adopted the method to generate the Walsh patterns in strict sequency ordering directly from the primary set of Rademacher functions. This method has been adopted as it is simpler and requires lesser hardware resources as compared to other methods reviewed. This method generates all the i Walsh functions at the same time, where i is the index of Walsh functions. As already stated, the sequency of a Walsh function is defined as the number of zero crossings in one cycle. In strict sequency order, each row has one more crossings between 1's and -1's than the row above. Thus, alternate even and odd patterns i.e. Cal-Sal patterns are obtained in this ordering. The various steps and algorithm for generation have been discussed as under.

#### Algorithm for Walsh pattern generation

In the algorithm for Walsh functions generation, the original 1's are kept, but -1's are replaced by 0, and all the Walsh functions are generated in the complete interval between 0 and 1 rather than between  $-\frac{1}{2}$  and  $\frac{1}{2}$ . After the changing of original symbols the basic properties like a modulo-2 addition of two Walsh functions yields another Walsh function hold for all the Walsh functions. To generate, we use the properties described above.

**Step-I:** Let  $\vec{B} = (b_{n-1}, b_{n-2}, \dots, b_j, \dots, b_0)$  be a binary vector representing an index of the Walsh function (i.e. the sequency), where  $0 \le j \le n-1$ .

**Step-II:** obtain the Gray code  $\vec{G} = (g_{n-1}, g_{n-2}, \dots, g_j, \dots, g_0)$  from the natural binary code

$\vec{B} = (b_{n-1}, b_{n-2}, \dots, b_j, \dots, b_0)$ , where  $g_j = b_{j+1} \oplus b_j$  for  $0 \le j \le n-2$ , and  $g_{n-1} = b_{n-1}$ .

**Step-III:** Generate the Walsh functions in strict sequency ordering as follows (*i* is the index of walsh patterns):

• Some of the Walsh patterns (say WR patterns) can be obtained directly from the Rademacher functions as

$$WR(2^{i+1}-1, k) = R_i(k) \quad (using \text{ property } 2.1)$$

$$W(0,k) = WR(0,k) = +1, \qquad \text{for all } k$$

• Remaining Walsh functions are obtained from these WR patterns as follows:

$$w(i) = \sum_{j=0}^{n-1} g_j WR(2^{j+1} - 1) = \sum_{j=0}^{n-1} g_j R_j, \quad (using \ property \ 2.4)$$

- While obtaining the patterns using the above equation, reduce any combinations of 3 or more Walsh functions (wherever possible) to combinations of two Walsh functions which have already been obtained in the sequence of patterns. (Using property 2.2 and 2.3)

- The Cal patterns are even functions having even sequency and Sal patterns are odd functions having odd sequency. Every even indexed ( $\vec{B}$  is even) walsh pattern i.e. the Cal pattern is to be complemented.

Figure 3.3-flow graph for Walsh patterns generation

# 3.2. SELECTION OF WALSH PATTERNS AND NOISE PATTERNS IN D-49 PIU:

In the following sections, the existing design for pattern selection in D-49 PIU has been highlighted and then the new design has been discussed.

# 3.2.1. Existing Design

The 128 Walsh patterns have been divided into two groups as *High Group* and *Low Group*. The control signals required for enabling/disabling Walsh Patterns, selection of *High Group* or *Low Group* and Noise ON/OFF are generated in the control PIU D-49 in the ABR at the base of each antenna . The Digital Plug-In-Unit (PIU), D-49 of the Local Oscillator (LO) Synthesiser in the ABR is the control PIU and contains the following PCBs:

- The MCM PCB, which is the interface to the LO systems.

- The Reset PCB RESET\_R1.

- The Control PCB CON\_R2.

- The Walsh and Noise Generator control PCB WNG\_RO with ID Code D 85, used in the Monitoring scheme of the synthesizer as well as controlling a few parameters of the front-end at the antenna.

- The Power supply PCB.

- The Monitor multiplexer PCB, MON32\_R0.

- The front panel LED indicator PCB, LED49\_R0.

A Block Diagram of the control PIU-D49 is shown in the following figure.

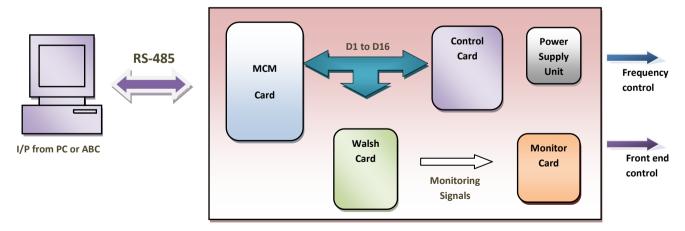

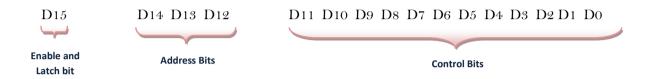

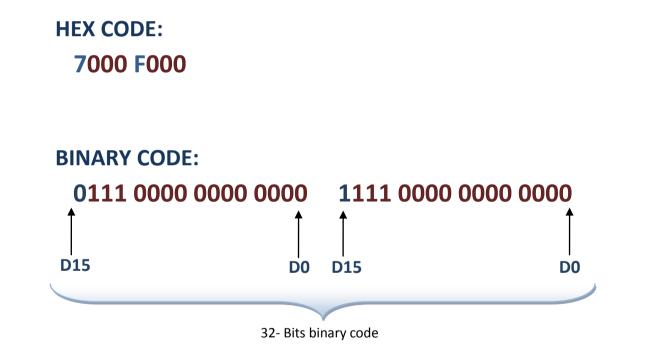

MCMs are general purpose microcontroller based cards which provide 16 TTL digital control outputs and can monitor up to 64 input analog signals. These MCMs are the interface to all the settable GMRT subsystems, like the front-ends, the LOs, the attenuators, etc. In detail, at each antenna, MCM 5 is the interface to the front end system, while MCMs 2, 3, and 9 are the interface to the LO and IF systems. Input to MCM card is provided from PC or ABC through a RS-485 line. These inputs are the various commands issued by a user for setting the parameters of the electronics and for monitoring a range of parameters. The 16 bit digital data from MCM card is divided into three parts as under:

The address bits for address are used to obtain, in principle a total of  $8\times12=96$  independent control bits. Also, the Enable and Latch bit helps in latching the data so that any Address Group can be set without worrying about the control bits already set through another address group.

- Address groups 0, 1, 2 and 4 are used for the control of GMRT synthesizer to set the required frequency. The controls under these groups are controlled using the Control card PCB.

- Address group 6 contains control bits used for monitoring. These controls are operated by the Walsh card PCB.

- Address group 7 contains control bits used for setting a few of the front-end parameters related to Walsh switching. The controls under this group are controlled by the Walsh card PCB.

- Address groups 3 and 5 are not used.

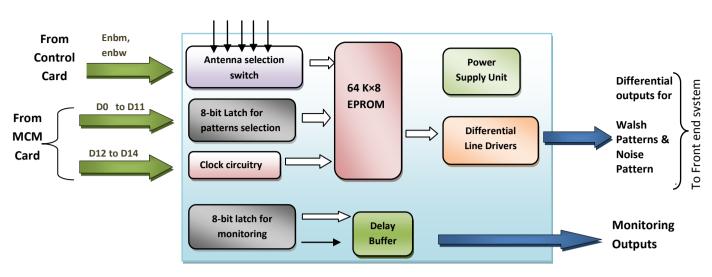

The digital data from MCM is available on 20 pin FRC Connector and then sent to control card PCB CON\_R2 and Walsh and noise generation PCB WNG\_R0. Depending on the address group selected (as stated above), Control card PCB or the Walsh card PCB comes into operation and gives the required outputs as per the control bits selected. Thus WNG\_R0 PCB comes into operation by group 6 and group 7 selections and is used for generating monitoring outputs and selection of noise ON/OFF or Walsh enable/disable respectively. The block diagram of the existing Walsh Card WNG\_R0 is as follows:

#### CHAPTER 3-Design and Development

Figure 3.5- Block Diagram of Walsh Card

# 3.2.2. New Design and Development

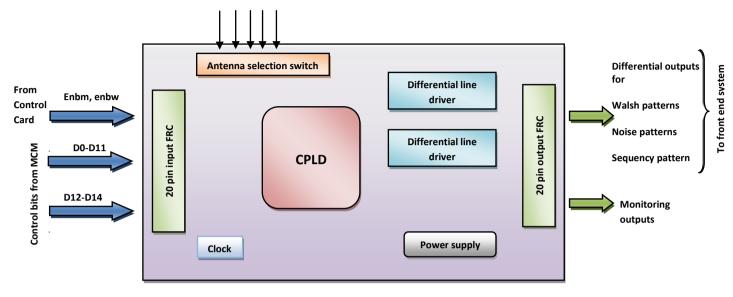

As per our project, we aim to use a CPLD based circuit for the functions under the group-7 and control of functions under group-6. Thus the CPLD has to be programmed with logic for these operations and to be placed in the Walsh card circuit along with few other components and digital IC's. In this section, we discuss the architecture and the logic synthesis and simulations for generating and selecting the various patterns on the new Walsh card. The main differences between the previous design and the new design are as follows:

- The heart of the new Walsh card circuit is a CPLD which contains the main logic for various pattern generation and selection instead of EPROM. The various advantages of using CPLD over EPROM have been discussed in the beginning.

- In case of the new Walsh card, we are generating a desired pattern based on the selection inputs at that particular instant, instead of storing them in advance.

- The new Walsh card can be used for generating only the Cal patterns or the Sal patterns, in comparison to the existing circuit which uses both the Cal and the Sal patterns.

- Additional functionality can easily be added by reprogramming the CPLD at any time in future to provide more flexibility to the users. Some of these additional modifications will be discussed in later sections.

The advantages of using a CPLD based Walsh card circuit are as follows:

Consist of a programmable Walsh pattern generator:

Instead of storing all the 128 Walsh patterns, Sequency pattern and noise pattern in advance, we now generate the desired pattern dynamically as per the requirements of the user. This will reduce the requirement of the resources for the operation.

Independent channel selection facility for taking the Walsh patterns output on any of the channels of an antenna:

The user can now have the provision to select independent channels of a particular antenna and add Walsh patterns on these channels as follows:

- To add Walsh pattern on one of the channels, i.e., Channel (CH1) 1 or Channel 2 (CH2) while disabling Walsh pattern on the other.

- To add different Walsh patterns on both the channels from Group-1 or Group-2. For CH-1 or CH-2, respectively, at the same time.

- To add the CH-1 Walsh pattern on CH-2.

- To add the CH-2 Walsh pattern on CH-2.

- ✤ Variable time period selection for all the patterns:

The complete 128 bits pattern for Walsh function, Sequency and the pattern for noise may be needed for certain time duration depending on the need of the user and the system. The new circuit thus gives the facility to select variable time period for each of the bits of these patterns. The user can select either a 4ms, 8ms, 16ms or 32ms duration time period each bit of every pattern.

#### Independent time period of noise patterns and Walsh patterns:

The length and time period of noise patterns and 128-bits Walsh patterns, sequency patterns is independent of each other, i.e., the time period of noise pattern can be varied while keeping the time period for Walsh pattern and sequency pattern constant and vice-versa.

✤ Only CAL patterns selection:

In order to remove the phase ambiguity between Cal and Sal patterns, only Cal patterns have been used for the antennae.

The new circuit consists of various blocks replacing the components in the previous Walsh card circuits which have been described above. The blocks are as follows:

- CPLD with core logic for various pattern generation and monitoring outputs.

- Differential line driver circuitry

Figure 3.6- Block diagram of new Walsh card

### Working of the circuit

- The 16 bit control bits D0-D14 are input to the Walsh card from the MCM card and the two latch enable bits enbw and enbm from the Control card, through the 20 pin input FRC. 'enbw' is the enable bit for the group 7 and 'enbm' is the enable bit for group 6. Both these bits are generated by a 3:8 decoder in the control card from D15-D12 bits coming from the MCM card.

- Antenna selection switch: A DIP-5 switch is used for selecting the antenna to be operated.

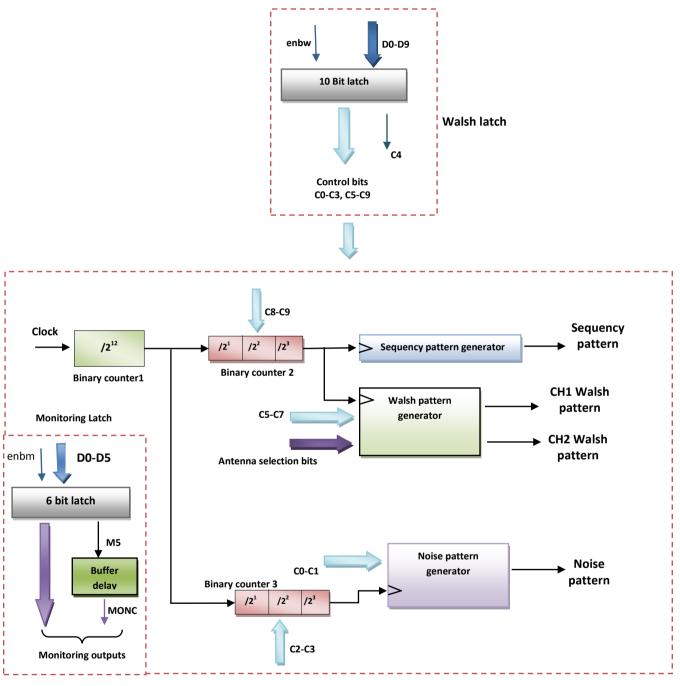

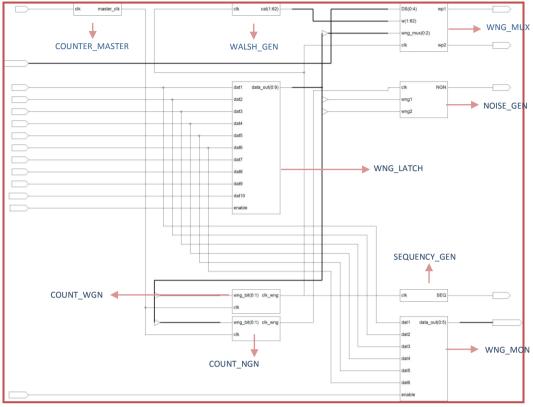

- <u>CPLD</u> is dedicated for pattern outputs and monitoring outputs. It consists of:

- <u>Walsh latch</u>: 10 bit latch used for latching the control bits D0 to D9. The remaining 2 bits D11-D12 are not used. It holds the control bits for clock frequency selection, Walsh pattern selection, channel selection, noise pattern selection, switching ON and OFF the front end MCM, and at the output; we obtain control bits C0-C9. It is enabled when group 7 has been selected after a low to high transition on 'enbw'. The output bit C4 is used for MCM ON/OFF.

- <u>Monitoring latch</u>: 6 bit latch for latching the control bits D0 to D5 for selecting monitoring signals and is enabled when group 6 has been selected after a low to high transition on 'enbm'. The latched out bits are the monitoring outputs.

- <u>Delay Buffer</u>: A Delay buffer is used for delaying one of the monitoring outputs from the 6-bit monitoring latch.

- <u>Clock Circuitry</u>: This is required for synchronizing all the components for pattern generation. Clock circuitry comprises of 1.024 MHz crystal oscillator and two 3 stage binary counters. Frequency division is required for various patterns to be ON/OFF for a fixed duration of time in order to synchronize with the system. Thus, an internal clock frequency division by  $2^{12}$  is needed which is further divided variably from  $2^1$  to  $2^3$ . The variable frequency division is selected using C2-C3 for noise generator and C8-C9 for Walsh generator. For  $F_{in} = 1.024$  MHz

| $F_1 = F_{21} = (1.024 \times 10^6) / 4096$ |                               |

|---------------------------------------------|-------------------------------|

| =250 Hz                                     | $T_1 = T_{21} = 4 \text{ ms}$ |

| $F_{22} = 250/2$                            |                               |

| =125 Hz                                     | $T_{21} = 8 \mathrm{\ ms}$    |

| F <sub>23</sub> =250/4                      |                               |

| =62.5 Hz                                    | $T_{22} = 16 \text{ ms}$      |

| $F_{24} = 250/2$                            |                               |

| =31.25 Hz                                   | $T_{23}$ =32 ms               |

- <u>Walsh pattern generator</u>: 128 patterns can be generated of length 128 bits each for both the channels of the 30 antennae and these are selected by combination of antenna selection bits. Clock input is from the binary counter for Walsh generator. The control bits C5-C7 are used for pattern selection on each of the channels. Each pattern is a 128 bit pattern.

- <u>Sequency pattern generator</u>: 128 bit pattern is generated for indicating start and stop of the Walsh pattern. It is to be synchronized with the Walsh patterns and hence same clock input is used as the Walsh pattern.

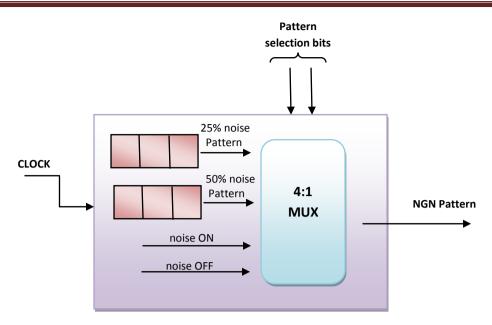

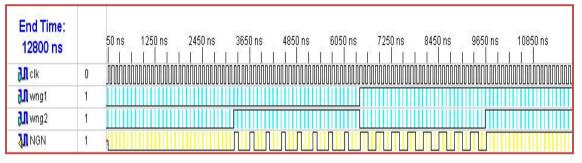

- <u>Noise generator</u>: NGN pattern is obtained at its output by combination of C0-C1. The clock input is from the binary counter for noise generator. It is independent of Walsh and Sequency patterns and can be switched ON/OFF at any time by changing the control bits combination.

- Differential line drivers: The patterns thus produced are processed in differential line drivers MC 3487, so that long lines to the front-end can be driven. Additional outputs of the pattern and Sequency are provided for retransmission to CEB through the LOR return link electronics. Differential line driver are required for transmitting the signals over long distance, such as from the antenna base to the front end. For each input, there are two differential outputs, where one is positive and the other one is its reverse. The Walsh patterns, Sequency pattern, noise pattern, MCM on/ off signal from the CPLD are sent through two differential line drivers giving a total of 8 signals at the output. At the frontend there is a differential line receiver IC MC3486 which recombines the differential input and then further processing is performed.

The following diagram shows the structure of the CPLD. Each block and its logic for implementation have been discussed in the following section.

Figure 3.7-structure for pattern generation circuitry (programmed in CPLD)

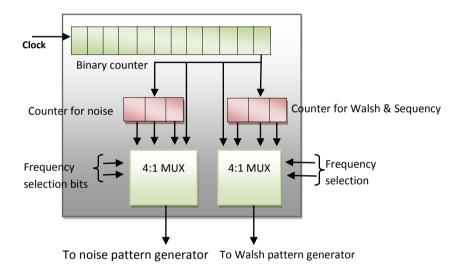

## Architecture for Clock circuitry

The clock circuitry consists of 3 binary counters as follows:

- One of the counters divides the incoming clock signal frequency from the clock oscillator by 2<sup>12</sup> (i.e. 4096). The divided clock signal now becomes the driving clock signal for rest of the circuit operation. The remaining two counters are 3 stage counters (counts from 0 to 127) used for dividing the above clock signal further by 2<sup>1</sup> or 2<sup>2</sup> or 2<sup>3</sup> or none.

- Two 4:1 multiplexers are to be used for selecting any one of the clock signals for walsh generator and noise generator, respectively.

- The select lines are the control bits C2-C3 for varying the clock frequency of the noise generator and C8-C9 are the select lines for varying the clock frequency of the Walsh and Sequency generator.

Figure 3.8-block diagram for clock circuitry

|                                                         |    | Table 3.1- Tr                  | uth Table for Clock | Circuitry                                                         |                      |  |

|---------------------------------------------------------|----|--------------------------------|---------------------|-------------------------------------------------------------------|----------------------|--|

| Frequency selection bits for<br>Noise pattern generator |    | Frequency sele<br>Walsh patter |                     | Selected Clock<br>frequency<br>(F <sub>in</sub> /2 <sup>n</sup> ) | Time period          |  |

| D3                                                      | D2 | D9                             | D8                  | n                                                                 | (1/F <sub>in</sub> ) |  |

| 0                                                       | 0  | 0                              | 0                   | 0                                                                 | 4 ms                 |  |

| 0                                                       | 1  | 0                              | 1                   | 1                                                                 | 8 ms                 |  |

| 1                                                       | 0  | 1                              | 0                   | 2                                                                 | 16 ms                |  |

| 1                                                       | 1  | 1                              | 1                   | 3                                                                 | 32 ms                |  |

|                                                         |    |                                |                     |                                                                   |                      |  |

Table 3.1- Truth Table for Clock Circuitry

$F_{in}=1.024$  Mhz

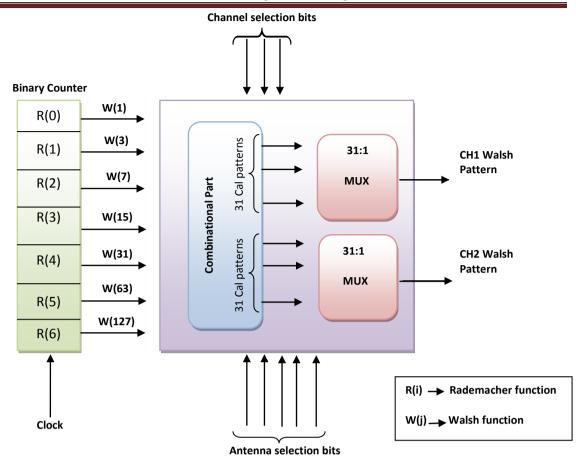

#### Architecture and Logic for Walsh Pattern Generator

We have discussed earlier that 128 Walsh patterns must be generated for each of the channels of 30 GMRT Antennae, where first and the last Walsh pattern in the series will not be used i.e. patterns w(0) and w(127) are not used. Thus, the index for Walsh patterns is 128. Thus, there are 63 pairs of Cal-Sal patterns for Walsh switching. But, we have decided to use only the Cal patterns for Walsh switching and hence the new circuit generates 62 Cal patterns at the output. The first 31 Cal patterns are grouped into Group-1 and the next 31 Cal patterns are grouped into Group-2. Out of these only 60 patterns are required for each of the 2 channels of the 30 antennae and so we actually require 60 Cal patterns from cal(1) to cal(60) which is w(2) to w(120), respectively (cal(0) is w(0)). The logic for Walsh function generator is based on the algorithm discussed in previous section. By implementing this algorithm, we can generate all the 128 patterns of 128 bit length, simultaneously and keep only 62 of these patterns. But at the output, we need only one pattern for each channel of the antenna which is obtained using a multiplexer. We obtain single bit-by-bit output at every clock cycle. The various blocks of the generator are as follows:

- 7 T Flip-Flops with positive edge triggering which form a binary counter to count from 0 to 127. At every low-high transition of the clock, each of the flip flops output bit is obtained forming Walsh-Rademacher patterns. After 127<sup>th</sup> counts, the counter is again reset to **0**.

- *XOR Gates* for performing modulo-2 summation between Rademacher patterns and other Walsh patterns. This forms the combinational part of the circuitry.

- *Two 31:1 multiplexers* for selecting Walsh patterns on individual channels. The select lines for these multiplexers are the antenna selection bits through Antenna selection switch.

- Combination of antenna selection bits is used as the input for selecting a corresponding Walsh pattern for that particular antenna.

- Control bits are used for channel selection for the selected antenna. C5-C7 used for channel selection.

CHAPTER 3-Design and Development

Figure 3.9-block diagram representing the architecture of Walsh pattern generator

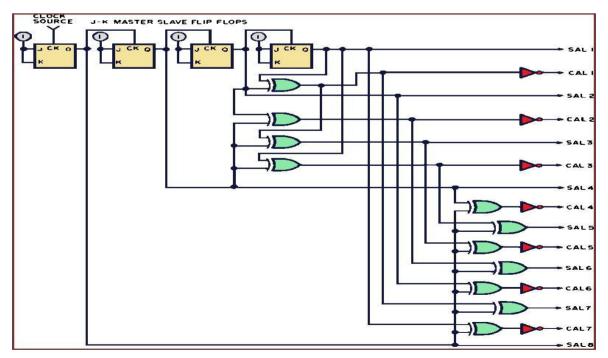

Figure 3.10-circuit diagram for generating 16 Walsh patterns

Figure 3.10 shows the circuit diagram for generation of set of 16 Walsh patterns. The same circuit has been used to generate 128 Walsh patterns by adding XOR gates and T- Flip Flops.

|     | Antenna selection Bits |     | on Bits |     | Chan | nel selectio | on bits | Cha       | nnel      |

|-----|------------------------|-----|---------|-----|------|--------------|---------|-----------|-----------|

| DS0 | D\$1                   | DS2 | DS3     | DS4 | D7   | D6           | D5      | CH1       | CH2       |

| Х   | Х                      | Х   | Х       | x   | 0    | 0            | 0       | WALSH OFF | WALSH OFF |

| 0   | 0                      | 0   | 0       | 0   | 0    | 0            | 1       | CAL 1     | WALSH OFF |

|     |                        |     |         |     | 0    | 1            | 0       | WALSH OFF | CAL 32    |

|     |                        |     |         |     | 0    | 1            | 1       | CAL 1     | CAL 32    |

|     |                        |     |         |     | 1    | 0            | 0       | CAL1      | CAL1      |

|     |                        |     |         |     | 1    | 0            | 1       | CAL32     | CAL32     |

| 0   | 0                      | 0   | 0       | 1   | 0    | 0            | 1       | CAL 2     | WALSH OFF |

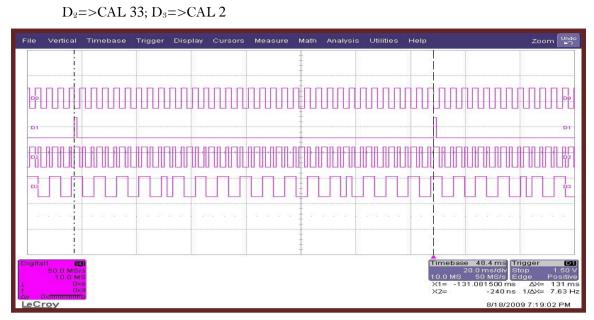

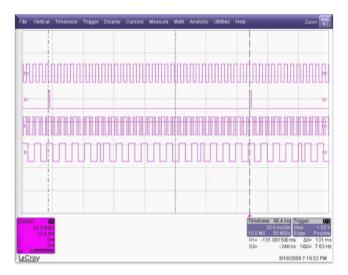

|     |                        |     |         |     | 0    | 1            | 0       | WALSH OFF | CAL 33    |

|     |                        |     |         |     | 0    | 1            | 1       | CAL 2     | CAL 33    |

|     |                        |     |         |     | 1    | 0            | 0       | CAL2      | CAL2      |

|     |                        |     |         |     | 1    | 0            | 1       | CAL33     | CAL33     |

| 0   | 0                      | 0   | 1       | 0   | 0    | 0            | 1       | CAL 3     | WALSH OFF |

|     |                        |     |         |     | 0    | 1            | 0       | WALSH OFF | CAL 34    |

|     |                        |     |         |     | 0    | 1            | 1       | CAL 3     | CAL 3     |

|     |                        |     |         |     | 1    | 0            | 0       | CAL3      | CAL3      |

|     |                        |     |         |     | 1    | 0            | 1       | CAL34     | CAL34     |

| 0   | 0                      | 0   | 1       | 1   | 0    | 0            | 1       | CAL 4     | WALSH OFF |

|     |                        |     |         |     | 0    | 1            | 0       | WALSH OFF | CAL 35    |

|     |                        |     |         |     | 0    | 1            | 1       | CAL 4     | CAL 35    |

|     |                        |     |         |     | 1    | 0            | 0       | CAL4      | CAL4      |

|     |                        |     |         |     | 1    | 0            | 1       | CAL35     | CAL35     |

| 0   | 0                      | 1   | 0       | 0   | 0    | 0            | 1       | CAL 5     | WALSH OFF |

| -   | -                      | _   | -       | -   | 0    | 1            | 0       | WALSH OFF | CAL 36    |

|     |                        |     |         |     | 0    | 1            | 1       | CAL 5     | CAL 36    |

|     |                        |     |         |     | 1    | 0            | 0       | CAL5      | CAL5      |

|     |                        |     |         |     | 1    | 0            | 1       | CAL36     | CAL36     |

| 0   | 0                      | 1   | 0       | 1   | 0    | 0            | 1       | CAL 6     | WALSH OFF |

| 0   | 0                      | 1   | 0       | 1   | 0    | 1            | 0       | WALSH OFF | CAL 37    |

|     |                        |     |         |     |      |              |         |           |           |

|     |                        |     |         |     | 0    | 1            | 1       | CAL 6     | CAL 37    |

|     |                        |     |         |     | 1    | 0            | 0       | CAL6      | CAL6      |

|     |                        |     |         |     | 1    | 0            | 1       | CAL37     | CAL37     |

| 0   | 0                      | 1   | 1       | 0   | 0    | 0            | 1       | CAL 7     | WALSH OFF |

|     |                        |     |         |     | 0    | 1            | 0       | WALSH OFF | CAL 38    |

|     |                        |     |         |     | 0    | 1            | 1       | CAL 7     | CAL 38    |

|     |                        |     |         |     | 1    | 0            | 0       | CAL7      | CAL7      |

|     |                        |     |         |     | 1    | 0            | 1       | CAL38     | CAL38     |

| 0   | 0                      | 1   | 1       | 1   | 0    | 0            | 1       | CAL 8     | WALSH OFF |

|     |                        |     |         |     | 0    | 1            | 0       | WALSH OFF | CAL 39    |

|     |                        |     |         |     | 0    | 1            | 1       | CAL 8     | CAL 39    |

|     |                        |     |         |     | 1    | 0            | 0       | CAL8      | CAL8      |

|     |                        |     |         |     | 1    | 0            | 1       | CAL39     | CAL39     |

| 0   | 1                      | 0   | 0       | 0   | 0    | 0            | 1       | CAL 9     | WALSH OFF |

|   |   |   |   |   | 0 | 1      | 0 | WALSH OFF      | CAL 40          |

|---|---|---|---|---|---|--------|---|----------------|-----------------|

|   |   |   |   |   | 0 | 1      | 1 | CAL 9          | CAL 40          |

|   |   |   |   |   | 1 | 0      | 0 | CAL9           | CAL9            |

|   |   |   |   |   | 1 | 0      | 1 | CAL40          | CAL40           |

| 0 | 1 | 0 | 0 | 1 | 0 | 0      | 1 | CAL 10         | WALSH OF        |

|   |   |   |   |   | 0 | 1      | 0 | WALSH OFF      | CAL 41          |

|   |   |   |   |   | 0 | 1      | 1 | CAL 10         | CAL 41          |

|   |   |   |   |   | 1 | 0      | 0 | CAL10          | CAL10           |

|   |   |   |   |   | 1 | 0      | 1 | CAL41          | CAL41           |

| 0 | 1 | 0 | 1 | 0 | 0 | 0      | 1 | CAL 11         | WALSH OF        |

|   |   |   |   |   | 0 | 1      | 0 | WALSH OFF      | CAL 42          |

|   |   |   |   |   | 0 | 1      | 1 | CAL 11         | CAL 42          |

|   |   |   |   |   | 1 | 0      | 0 | CAL11          | CAL11           |

|   |   |   |   |   | 1 | 0      | 1 | CAI 42         | CAL42           |

| 0 | 1 | 0 | 1 | 1 | 0 | 0      | 1 | CAL 12         | WALSH OF        |

|   |   |   |   |   | 0 | 1      | 0 | WALSH OFF      | CAL 43          |

|   |   |   |   |   | 0 | 1      | 1 | CAL 12         | CAL 43          |

|   |   |   |   |   | 1 | 0      | 0 | CAL12          | CAL12           |

|   |   |   |   |   | 1 | 0      | 1 | CAL43          | CAL43           |

| 0 | 1 | 1 | 0 | 0 | 0 | 0      | 1 | CAL 13         | WALSH OF        |

|   |   |   |   |   | 0 | 1      | 0 | WALSH OFF      | CAL 44          |

|   |   |   |   |   | 0 | 1      | 1 | CAL 13         | CAL 44          |

|   |   |   |   |   | 1 | 0      | 0 | CAL13          | CAL13           |

|   |   |   |   |   | 1 | 0      | 1 | CAL44          | CAL44           |

| 0 | 1 | 1 | 0 | 1 | 0 | 0      | 1 | CAL 14         | WALSH OF        |

|   |   |   |   |   | 0 | 1      | 0 | WALSH OFF      | CAL 45          |

|   |   |   |   |   | 0 | 1      | 1 | CAL 14         | CAL 45          |

|   |   |   |   |   | 1 | 0      | 0 | CAL14          | CAL14           |

|   |   |   |   |   | 1 | 0      | 1 | CAL45          | CAL45           |

| 0 | 1 | 1 | 1 | 0 | 0 | 0      | 1 | CAL 15         | WALSH OF        |

| - | _ | _ | - | - | 0 | 1      | 0 | WALSH OFF      | CAL 46          |

|   |   |   |   |   | 0 | 1      | 1 | CAL 15         | CAL 46          |

|   |   |   |   |   | 1 | 0      | 0 | CAL15          | CAL15           |

|   |   |   |   |   | 1 | 0      | 1 | CAL46          | CAL46           |

| 0 | 1 | 1 | 1 | 1 | 0 | 0      | 1 | CAL 16         | WALSH OF        |

| 0 | - | - | - | - | 0 | 1      | 0 | WALSH OFF      | CAL 47          |

|   |   |   |   |   | 0 | 1      | 1 | CAL 16         | CAL 47          |

|   |   |   |   |   | 1 | 0      | 0 | CAL16          | CAL16           |

|   |   |   |   |   | 1 | 0      | 1 | CAL47          | CAL47           |

| 1 | 0 | 0 | 0 | 0 | 0 | 0      | 1 | CAL 17         | WALSH OF        |

| - | Ū | Ū | 0 | Ū | 0 | 1      | 0 | WALSH OFF      | CAL 48          |

|   |   |   |   |   | 0 | 1      | 1 | CAL 17         | CAL 48          |

|   |   |   |   |   | 1 |        | 0 | CAL17          | CAL 48<br>CAL17 |

|   |   |   |   |   | 1 | 0<br>0 | 1 | CAL17<br>CAL48 | CAL17<br>CAL48  |

| 1 | 0 | 0 | 0 | 1 |   |        |   |                |                 |

| 1 | 0 | 0 | 0 | 1 | 0 | 0      | 1 | CAL 18         | WALSH OF        |

|   |   |   |   |   | 0 | 1      | 0 | WALSH OFF      | CAL 49          |

|   |   |   |   |   | 0 | 1      | 1 | CAL 18         | CAL 49          |

|   |   |   |   |   | 1 | 0      | 0 | CAL18          | CAL18           |

|   |   | - |   |   | 1 | 0      | 1 | CAL49          | CAL49           |

| 1 | 0 | 0 | 1 | 0 | 0 | 0      | 1 | CAL 19         | WALSH OF        |

|   |   |   |   |   | 0 | 1      | 0 | WALSH OFF      | CAL 50          |

|   |   |   |   |   | 0 | 1      | 1 | CAL 19         | CAL 50          |

|   |   |   |   |   | 1 | 0      | 0 | CAL19          | CAL19           |

|   |   |   |   |   | 1 | 0 | 1 | CAL50            | CAL50          |

|---|---|---|---|---|---|---|---|------------------|----------------|

| 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | CAL 20           | WALSH OFF      |

|   |   |   |   |   | 0 | 1 | 0 | WALSH OFF        | CAL 51         |

|   |   |   |   |   | 0 | 1 | 1 | CAL 20           | CAL 51         |

|   |   |   |   |   | 1 | 0 | 0 | CAL20            | CAL20          |

|   |   |   |   |   | 1 | 0 | 1 | CAL51            | CAL51          |

| 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | CAL 21           | WALSH OFF      |

|   |   |   |   |   | 0 | 1 | 0 | WALSH OFF        | CAL 52         |

|   |   |   |   |   | 0 | 1 | 1 | CAL 21           | CAL 21         |

|   |   |   |   |   | 1 | 0 | 0 | CAL21            | CAL52          |

|   |   |   |   |   | 1 | 0 | 1 | CAL52            | CAL52          |

| 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | CAL 22           | WALSH OFF      |

| - | 0 | - | Ū | - | 0 | 1 | 0 | WALSH OFF        | CAL 53         |

|   |   |   |   |   | 0 | 1 | 1 | CAL 22           | CAL 53         |

|   |   |   |   |   | 1 | 0 | 0 | CAL 22<br>CAL 22 | CAL 33         |

|   |   |   |   |   | 1 | 0 | 1 | CAL22<br>CAL53   | CAL22<br>CAL53 |

| 1 | 0 | 1 | 1 | 0 | 0 | 0 | 1 |                  | WALSH OFF      |

| 1 | 0 | 1 | T | U |   |   |   | CAL 23           |                |

|   |   |   |   |   | 0 | 1 | 0 | WALSH OFF        | CAL 54         |

|   |   |   |   |   | 0 | 1 | 1 | CAL 23           | CAL 23         |

|   |   |   |   |   | 1 | 0 | 0 | CAL23            | CAL54          |

|   |   |   |   |   | 1 | 0 | 1 | CAL54            | CAL54          |

| 1 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | CAL 24           | WALSH OFF      |

|   |   |   |   |   | 0 | 1 | 0 | WALSH OFF        | CAL 55         |

|   |   |   |   |   | 0 | 1 | 1 | CAL 24           | CAL 55         |

|   |   |   |   |   | 1 | 0 | 0 | CAL24            | CAL24          |

|   |   |   |   |   | 1 | 0 | 1 | CAL55            | CAL55          |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | CAL 25           | WALSH OFF      |

|   |   |   |   |   | 0 | 1 | 0 | WALSH OFF        | CAL 56         |

|   |   |   |   |   | 0 | 1 | 1 | CAL 25           | CAL 56         |

|   |   |   |   |   | 1 | 0 | 0 | CAL25            | CAL25          |

|   |   |   |   |   | 1 | 0 | 1 | CAL56            | CAL56          |

| 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | CAL 26           | WALSH OFF      |

|   |   |   |   |   | 0 | 1 | 0 | WALSH OFF        | CAL 57         |

|   |   |   |   |   | 0 | 1 | 1 | CAL 26           | CAL 57         |

|   |   |   |   |   | 1 | 0 | 0 | CAL26            | CAL26          |

|   |   |   |   |   | 1 | 0 | 1 | CAL57            | CAL57          |

| 1 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | CAL 27           | WALSH OFF      |

|   |   |   |   |   | 0 | 1 | 0 | WALSH OFF        | CAL 58         |

|   |   |   |   |   | 0 | 1 | 1 | CAL 27           | CAL 58         |

|   |   |   |   |   | 1 | 0 | 0 | CAL27            | CAL26          |

|   |   |   |   |   | 1 | 0 | 1 | CAL58            | CAL58          |

| 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | CAL 28           | WALSH OFF      |

|   |   |   |   |   | 0 | 1 | 0 | WALSH OFF        | CAL 59         |

|   |   |   |   |   | 0 | 1 | 1 | CAL 28           | CAL 59         |

|   |   |   |   |   | 1 | 0 | 0 | CAL28            | CAL28          |

|   |   |   |   |   | 1 | 0 | 1 | CAL59            | CAL59          |

| 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | CAL 29           | WALSH OFF      |

|   |   |   |   |   | 0 | 1 | 0 | WALSH OFF        | CAL 60         |

|   |   |   |   |   | 0 | 1 | 1 | CAL 29           | CAL 60         |

|   |   |   |   |   | 1 | 0 | 0 | CAL29            | CAL29          |

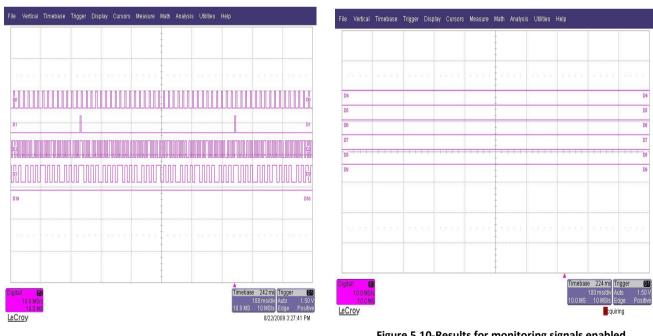

|   |   |   |   |   | 1 | 0 | 1 | CAL60            | CAL60          |