# VHDL Implementation of Optimized RFI Detection System Proposed for SKA

Student Project

By

Aditya Mathuriya

Electronics and Communication Engineering SardarVallabhai National Institute of Technology, Surat

Under the Guidance of

Mr. Kaushal D. Buch

### GIANT METREWAVE RADIO TELESCOPE NATIONAL CENTER FOR RADIO ASTROPHYSICS TATA INSTITUTE OF FUNDAMENTAL RESEARCH

Narayangaon, Tal-Junnar, Dist-Pune May 2023- July 2023

# **Acknowledgments**

I would like to express my heartfelt appreciation and gratitude to my mentor, Mr. Kaushal D. Buch, Engineer F, Digital Backend Group, GMRT, for their invaluable guidance, encouragement, and insightful suggestions throughout this project. Their unwavering support and teachings were instrumental in the completion of this report. I am deeply grateful for their constant assistance and direction.

I extend my thanks to Mr. B. Ajith Kumar, Group Coordinator, GMRT Backend Group, for his cooperation, support, and permission to work within the Digital Back-end Group.

I would like to express my sincere appreciation to the members of the Digital Backend group and the entire staff of GMRT. Every interaction with them has been a valuable learning experience, and their motivation has been instrumental in keeping me inspired and focused on my work.

~Aditya Mathuriya

# Contents

| Abstract                                 | 8  |

|------------------------------------------|----|

| 1.1 Overview                             | 9  |

| 1.3 RFI Filtering at GMRT                |    |

| 1.4 Square Kilometer Array (SKA)         | 12 |

| 1.5 Tile Processing Module               | 12 |

| Chapter 02: MAD/MOM Based RFI MITIGATION | 14 |

| 2.1 MAD                                  | 14 |

| 2.2 MoM                                  | 14 |

| 2.3 VHDL Implementation of Filters       | 15 |

| 2.4 Application of RFI Filters in TPM    | 18 |

| 2.5 Need for Optimization                | 21 |

| Chapter 03: Analysis of TPM Data         | 22 |

| 3.1 Data Format                          | 22 |

| 3.2 Python Tool                          | 23 |

| 3.3 Flowchart of Tool                    | 24 |

| 3.4 Time Domain Analysis                 | 25 |

| 3.5 Frequency Domain Analysis            | 28 |

| Chapter 04: Optimization                 | 31 |

| 4.1 Optimized MAD Multiplexed Design     | 31 |

| 4.1.1 Synthesis and Implementation       | 33 |

| 4.1.2 Timing Details                     | 34 |

| 4.1.3 Utilization details                | 34 |

| 4.2 Optimized MOM Multiplexed Design     | 36 |

| 4.2.1 Synthesis and Implementation       | 38 |

| 4.2.2 Timing Details                     | 39 |

| 4.2.3 Utilization Details                | 39 |

| 4.3 Single MAD Design                    | 41 |

| 4.3.1 Synthesis and Implementation       | 44 |

| 4.3.2 Timing Details                     | 45 |

| 4.3.3 Utilization Details                | 45 |

| 4.4 Single MoM Design                    | 47 |

| 4.4.1 Synthesis and Implementation               | 49 |

|--------------------------------------------------|----|

| 4.4.2 Timing Details                             | 50 |

| 4.4.3 Utilization Details                        | 50 |

| Chapter 05: Further Optimization                 | 52 |

| 5.1 Synthesis and Implementation                 | 54 |

| 5.2 Timing Details                               | 55 |

| 5.3 Utilization Details                          | 55 |

| Chapter 06: Resource Comparison and Verification | 57 |

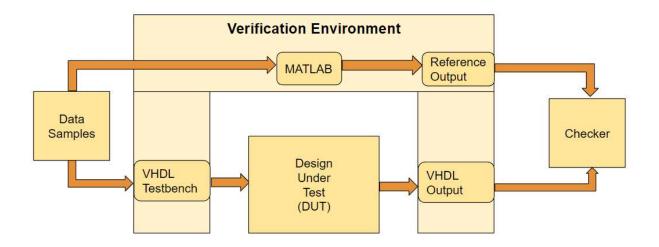

| Verification with Matlab                         | 58 |

| VHDL Testbench                                   | 59 |

| Conclusion and Future Scope                      | 60 |

| References                                       | 61 |

| Appendix                                         | 62 |

| Generic value to be defined in top entity        | 62 |

| Versions of Designs                              | 62 |

| Output Comparison Table                          | 63 |

# List Of Figures

| Figure 1.1 GMRT Antennas (courtesy NCRA Archives)                                      | 9  |

|----------------------------------------------------------------------------------------|----|

| Figure 1.2 Distribution of Radio Signals Received From Space (courtesy globalsino.com) | 11 |

| Figure 1.3 Narrowband RFI (Courtesy: Mayuresh Surnis)                                  | 12 |

| Figure 1.4 Broadband RFI                                                               | 13 |

| Figure 2.1 Flowchart MAD Computation                                                   | 14 |

| Figure 2.2 Flowchart of MoM Computation                                                | 15 |

| Figure 2.2 Histogram-based Median Calculation.                                         | 16 |

| Figure 2.3 Median Absolute Deviation (MAD) Computation                                 | 16 |

| Figure 2.4 Block Diagram of MoM Computation                                            | 17 |

| Figure 2.4 Input-Output View of Top Module                                             | 18 |

| Figure 2.5 Block Diagram of MAD/MoM Multiplexed Architecture                           | 19 |

| Figure 2.6 Single MAD / MOM Multiple Detection                                         | 20 |

| Figure 3.1 Flowchart of Tool.                                                          | 24 |

| Figure 3.2 Time domain analysis                                                        | 25 |

| Figure 3.3 MoM with 2k window size                                                     | 26 |

| Figure 3.4 MoM with 4k window size                                                     |    |

| Figure 3.5 MoM with 8k window size                                                     | 27 |

| Figure 3.6 Cross-Correlation Spectrum                                                  | 28 |

| Figure 3.7 Power Spectrum Overlay for Unfiltered and Filtered Data                     | 29 |

| Figure 3.8 Average Power Spectrum for unfiltered and filtered data                     | 29 |

| Figure 3.9 Average Power Spectrum                                                      | 30 |

| Figure 4.2 Implementation View of MAD Multiplexed Design                               | 33 |

| Figure 4.2 Timing Report MAD Multiplexed                                               | 34 |

| Figure 4.3 CLB Utilization MAD Multiplexed                                             |    |

| Figure 4.4 Utilization Report of MAD Multiplexed                                       | 35 |

| Figure 4.5 Implementation view of MoM Multiplexed Design                               | 38 |

| Figure 4.6 Timing Report MoM Multiplexed                                               | 39 |

| Figure 4.7 CLB Logic MoM Multiplexed                                                   | 39 |

| Figure 4.8 Utilization Report of MoM Multiplexed                                 | 40 |

|----------------------------------------------------------------------------------|----|

| Figure 4.9 Single MAD / MOM Multiple Detection                                   | 41 |

| Figure 4.10 Implementation View of Single MAD Design                             | 44 |

| Figure 4.11 Timing Report Single MAD                                             | 45 |

| Figure 4.12 CLB Logic Single MAD                                                 | 45 |

| Figure 4.13 Utilization Report Single MAD                                        | 46 |

| Figure 4.14 Implementation View of Single MoM Design                             | 49 |

| Figure 4.15 Timing Report Single MoM                                             | 50 |

| Figure 4.16 CLB Logic Single MoM                                                 | 50 |

| Figure 4.17 Utilization Report of Single MoM                                     | 51 |

| Figure 5.1 Implementation View of MAD Multiplexed first Median zero              | 54 |

| Figure 5.2 Clock Summary MAD Multiplexed first Median zero                       | 55 |

| Figure 5.4 Utilization Report MAD Multiplexed first Median zero                  | 56 |

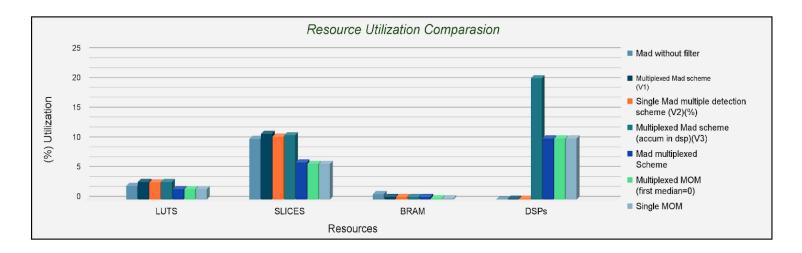

| Figure 6.1 Graphical Comparison of Resource Utilization across different methods | 57 |

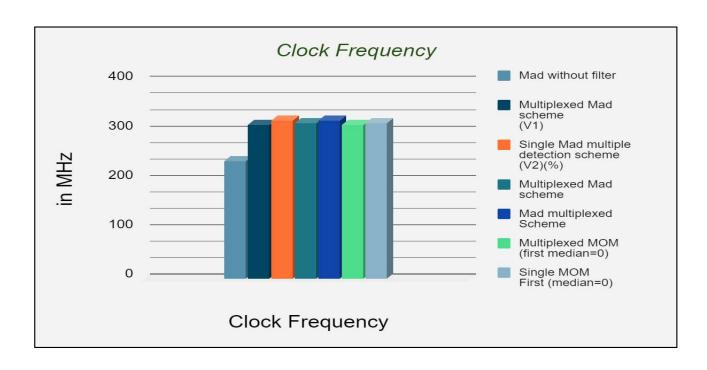

| Figure 6.2 Clock Frequency for different schemes                                 | 58 |

| Figure 6.3 Verification Environment                                              | 59 |

# List of Tables

| Table 2.1 Resource Utilization Table (16k window)                      | 21 |

|------------------------------------------------------------------------|----|

| Table 4.1 Resource Utilization MAD Multiplexed                         | 31 |

| Table 4.2 VHDL interface of Multiplexed MAD design                     | 32 |

| Table 4.3 Resource Utilization Multiplexed MoM Design                  | 36 |

| Table 4.4 VHDL interface of MOM multiplexed design                     | 37 |

| Table 4.5 Resource Utilization for Single MAD design                   | 42 |

| Table 4.6 VHDL interface of Single MAD design                          | 43 |

| Table 4.7 Resource utilization Single MoM                              | 47 |

| Table 4.8 VHDL interface of Single MOM design                          | 48 |

| Table 5.1 Resource Utilization MAD Multipltiplexed with first median 0 |    |

| Table 5.2 VHDL interface of MAD multiplexed design with zero median    | 53 |

| Table 6.1 Clock Frequency comparison                                   | 57 |

| Table A.1 Generic Description                                          | 62 |

| Table A.2 Versions of Design                                           | 63 |

| Table A.3 Output Comparison.                                           |    |

## **Abstract**

Radio Astronomy faces a formidable challenge in the form of Radio Frequency Interference (RFI), which severely affects the already weak radio signals under observation. To address this pressing issue, there is an urgent need to develop effective techniques for RFI mitigation. The objective of this project is to design an optimized architecture that enables the integration of previously developed Median Absolute Deviation (MAD) and Median-of-MAD (MoM) filters into the Tile Processing Module (TPM) beamformer design with the available hardware

resources on the FPGA. Additionally, this project aims to analyze the TPM raw voltage data

taken at the site and determine an optimal window size for the effective detection of RFI.

To enhance the architecture's resource utilization aspect, careful consideration was taken in the utilization of inbuilt units such as DSP slices. The selection of these units was specifically tailored to ensure optimal utilization of the TPM board's resources. By maximizing the utilization of available board resources, we aimed to achieve the highest possible efficiency and performance within the architecture.

The implementations of these methods were conducted on the Xilinx Kintex Ultrascale (part no xcku9p-ffve900-1-i) FPGA device. To validate the design, the same algorithm was also implemented in MATLAB as the golden reference model. Functional verification of the design was performed using MATLAB implementation, ensuring the accuracy and reliability of the proposed approach.

# Chapter 01: Introduction to GMRT and RFI

#### 1.1 Overview

The GMRT, which stands for Giant Metrewave Radio Telescope, is a powerful radio telescope located near Pune, India. It is operated by the National Centre for Radio Astrophysics (NCRA) of the Tata Institute of Fundamental Research (TIFR). The GMRT is one of the world's largest and most sensitive radio telescopes operating at meter wavelengths.[1]

The GMRT consists of an array of 30 antennas, each antenna is 45 meters in diameter. These antennas operate at different frequencies ranging from 150 MHz to 1450 MHz. The GMRT utilizes a novel antenna construction technique called SMART, with wire mesh panels and rope trusses for a lightweight and low wind-loading design, enabling economical construction of the entire array.

Figure 1.1 GMRT Antennas (courtesy NCRA Archives)

The GMRT Backend team focuses on developing the correlator and has also undertaken projects to address interference reduction, temperature monitoring, and other enhancements for the GMRT project. Following the establishment of the upgraded GMRT known as uGMRT, the primary processing takes place concurrently at 400 MHz and 32 MHz. This advanced system, referred to as the GMRT Wideband Backend (GWB), is responsible for handling the extensive data processing requirements at the telescope.

#### 1.3 RFI Filtering at GMRT

RFI, or Radio Frequency Interference, refers to unwanted electromagnetic signals or noise that can disrupt or degrade the quality of radio frequency signals used in communication systems, including wireless devices, radios, and radar systems. RFI can originate from various sources, such as power lines, electrical equipment, electronic devices, and even natural phenomena like lightning. The presence of RFI can lead to signal distortion, reduced dynamic range, and increased error rates in communication systems.

Figure 1.2 Distribution of Radio Signals Received From Space (courtesy globalsino.com)

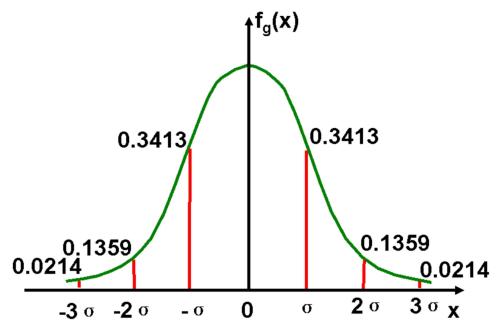

The radio signals received from celestial objects follow a normal distribution, as depicted in the Figure 1.2. However, these signals are susceptible to interference from RFI, which is primarily a local phenomenon. The amplitude of RFI is typically stronger than that of the astronomical signal, resulting in the useful signal being concentrated primarily within the range of  $-3\sigma$  to  $+3\sigma$ ,

at the center of the distribution curve. So the signals out of this range which have high amplitude are excised using different algorithms.

To mitigate RFI we at GMRT employ various algorithms like MAD (Median of Absolute Deviation) filtering and Median-of-MAD (MoM) filtering. These algorithms have been implemented on FPGA and are being used for real-time filtering of RFI [2].

#### 1.3.1 Narrowband RFI

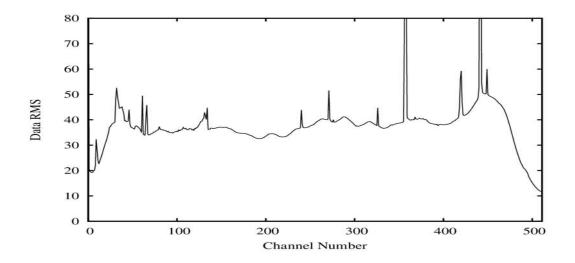

Narrowband radio frequency interference (RFI) typically manifests within a specific and limited portion of the electromagnetic spectrum. This particular type of signal tends to maintain its consistency over an extended period and generally does not result in any lasting harm to the system. Narrowband RFI often arises from the overlapping frequencies emitted by mobile towers and various communication devices. In Figure 1.3 presented below, the depicted narrow peaks illustrate the occurrence of narrowband RFI within the 325MHz observing band of GMRT.

Figure 1.3 Narrowband RFI (Courtesy: Mayuresh Surnis)

#### 1.3.2 Broadband RFI

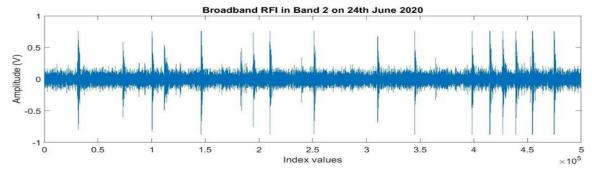

Impulsive RFI refers to a type of interference characterized by sudden bursts of high-energy signals, which can overpower and obscure the desired astronomical signals. It occurs in a brief

and sporadic manner, typically within a short time frame. Broadband RFI signals, on the other hand, possess a wide frequency range and have the potential to cause lasting harm to electronic receiver systems due to their intense nature. In Figure 1.4 displayed below, the depicted RFI exemplifies the presence of broadband interference observed at GMRT, primarily attributed to high voltage power lines, hence commonly referred to as powerline RFI.

Figure 1.4 Broadband RFI

#### 1.4 Square Kilometer Array (SKA)

The SKA (Square Kilometer Array) is an international project aimed at building the world's largest and most sensitive radio telescope. It will consist of thousands of radio antennas distributed across multiple continents, working together as a single integrated instrument. The SKA will be capable of observing the universe in unprecedented detail and sensitivity, enabling scientists to address fundamental questions about the nature of the universe, the formation of galaxies, the evolution of cosmic magnetism, and the search for extraterrestrial life. The project is a collaboration of over 20 countries and is expected to revolutionize our understanding of the universe through its cutting-edge technology and vast observation capabilities.

Indian astronomers with wide-ranging experience in low-frequency radio astronomy in a variety of astronomical phenomena and targets would be particularly well-placed to pursue time-critical transient objects with SKA and observatories at other bands[3].

## 1.5 Tile Processing Module

The signal processing in LFAA would be carried out using FPGA-based Tile Processing Module (TPM) developed by the Italian team for implementing the beamforming system. The Tile Processing Module is an essential component that performs multiple tasks, including data acquisition, channelization, and beamforming for the SKA Low-Frequency Aperture Array

instrument. It is designed to handle these operations for a set of 16 antennas, enabling the efficient processing of signals received by the instrument. The data that is received by TPM is sampled at a frequency of 800 MHz [4] A similar setup has been made at GMRT for testing purposes, and we have developed a technique similar to that used for mitigating RFI in real-time in the Upgraded GMRT (uGMRT)backend.

## **Chapter 02: MAD/MOM Based RFI MITIGATION**

The Median Absolute Deviation (MAD) is a way to measure how spread out or diverse a set of numbers is. To calculate MAD, we first find the middle value in the set, which is called the median. Then, we look at each number in the set and find the difference between that number and the median, always using positive values. We find the median of these differences to get the MAD which is helpful when we have numbers that are far away from the others, or when the numbers don't follow a typical pattern. For MoM computation, three Median computations are required. Further, both techniques have been explained in brief in sections 2.1 and 2.2

#### 2.1 MAD

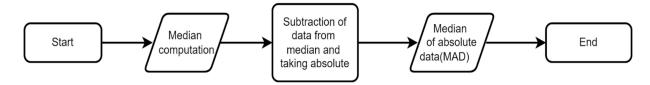

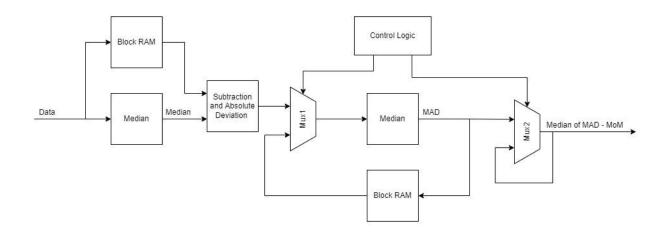

The process of calculating the MedianAbsolute Deviation (MAD) is depicted in Figure 2.1, which offers a comprehensive overview of the steps involved.

Figure 2.1 Flowchart MAD Computation

The first Median value is subtracted from the input data value. The absolute value of this difference is taken. If the difference is negative, then the two's complement is taken for conversing to absolute value. Then the second median of these absolute values is computed using the same algorithm, and it is called Median Absolute Deviation (MAD). For a dataset **X** having window size W, MAD can be computed as

MAD = median(

$$| X_i - median(X) |$$

)

$i = 1, 2, 3, ..., W$

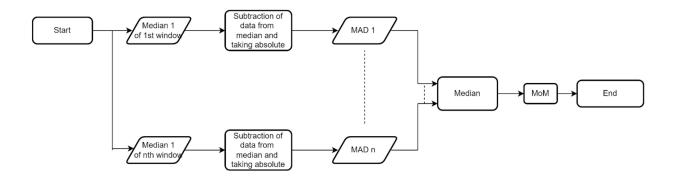

#### 2.2 MoM

For MoM computation, three Median computations are required. For real-time performance, it is challenging to buffer these data values. So, the calculated current MoM value is applied to the next cycle. Also, to optimize median computation, the third median computation is multiplexed with the second median computation see Figure 2.3. It is useful especially when the dataset is

large or when traditional sorting methods may be inefficient. The MoM technique involves dividing the dataset into smaller subgroups and finding the MAD within each subgroup. These subgroup MADs are then treated as a new set of data points and their median is computed.

$MoM = median (MAD_1, MAD_2, MAD_3,....MAD_n)$

where n = MoM window size

Figure 2.2 Flowchart of MoM Computation

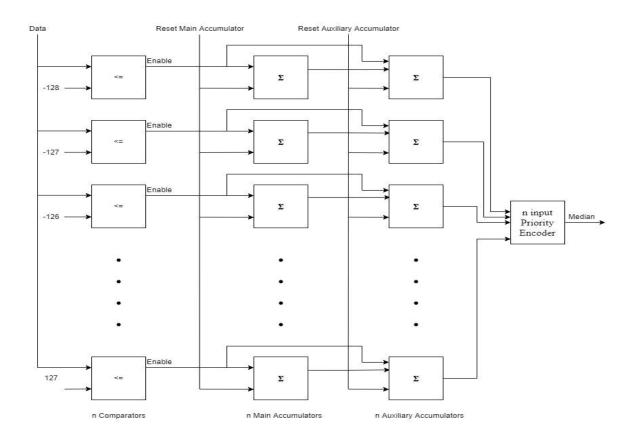

#### 2.3 VHDL Implementation of Filters

The present report focuses on the integration of previously developed Median Absolute Deviation (MAD) and Median of MAD (MoM) based RFI (Radio Frequency Interference) filters using VHDL (Very High-Speed Integrated Circuit Hardware Description Language). In the previous project, these filters were implemented individually for RFI mitigation. Both MAD and MoM filters were implemented for various window sizes i.e. 4k, 8k, and 16k.

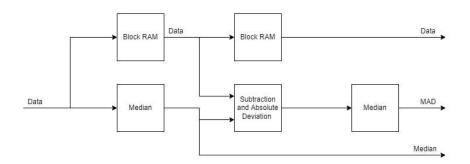

The method utilized in this project for finding the median of the window data is the Histogram method. Initially, the median is determined for the window data, and this value is then subtracted from each element within the window(see Figure 2.2)[5]. The resulting elements are converted to unsigned integers. Subsequently, the median of the updated window is calculated, which serves as the MAD value for the data window. The calculated median and MAD values are utilized to derive the threshold value for the signal(see Figure 2.3). To determine the window's variance, the MAD value is multiplied by a constant factor of 1.4826. The positive and negative thresholds are established by adding and subtracting the median value, respectively. Once the threshold values are obtained for one channel, the data from all channels are compared and flagged. User-defined criteria determine the replacement of the flagged data.[5]

Figure 2.2 Histogram-based Median Calculation

Figure 2.3 Median Absolute Deviation (MAD) Computation

Another approach employed in this project is the MoM method, which utilizes the MoM value to compute the threshold values.

Figure 2.4 Block Diagram of MoM Computation

The design implementation utilizes Xilinx Vivado version 2019.1 and is targeted for deployment on the *Xilinx Kintex Ultrascale (xcku9p-ffve900-1-i) FPGA* board. MATLAB software is employed for functional verification of the algorithm.

Verification of these filters was done by comparing the outputs with the MATLAB output (golden reference).

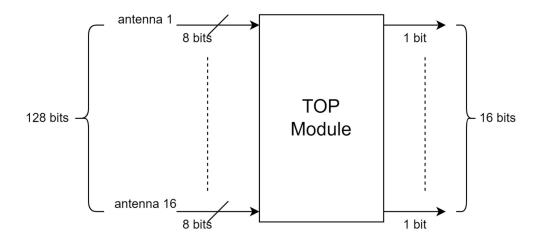

#### 2.4 Application of RFI Filters in TPM

The Tile Processing Module (TPM) comprises 16 antennas on a single tile. In our project, we aim to use RFI filters to identify windows that exhibit a high count of RFI. If the RFI count exceeds a specified reference value, the RFI flag is raised, indicating that the preceding data contains significant RFI and an appropriate action should be taken for subsequent processing. This approach allows us to effectively detect and flag data with substantial RFI content, enabling us to mitigate the impact of interference on further data analysis.

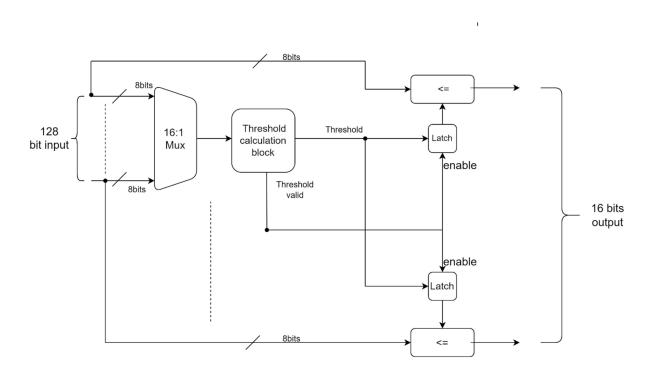

The TPM module receives inputs from 16 antennas, a total of 128 bits i.e. 8-bit for each antenna, as shown in Figure 2.4. The module processes this input and generates a 1-bit output for each antenna, resulting in a total of 16 bits of output.

Figure 2.4 Input-Output View of Top Module

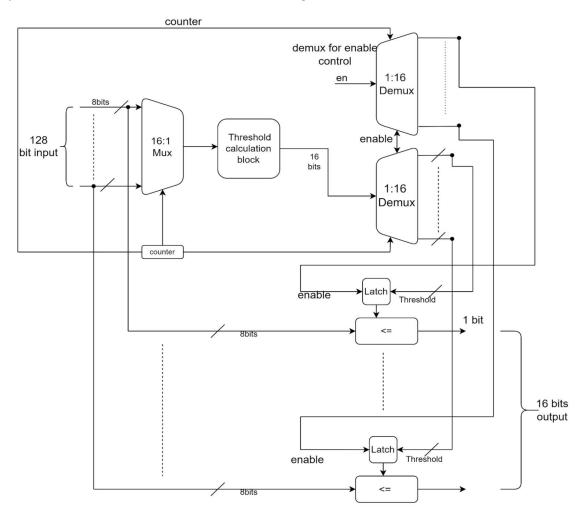

Based on the computed MAD or MoM values, the upper and lower thresholds are determined. If the incoming data falls outside these threshold boundaries, it is identified as RFI, resulting in an increment of the RFI counter. At the end of the window cycle, if the counter exceeds the reference value, the RFI flag is triggered, indicating the presence of highly corrupted data.

Due to limited FPGA resources, instead of having individual RFI filters for all 16 antennas simultaneously, a round-robin approach was implemented. In this approach, the thresholds are calculated sequentially, starting from the first antenna and moving to the next antenna cyclically. The updated thresholds for the first antenna are obtained once all 16 antennas have had their thresholds calculated. To facilitate this process, multiplexers are used to select the appropriate

antenna for threshold calculation, and the data flow is directed to the threshold calculation block. The calculated thresholds are then passed through a demultiplexer and stored in latches, ensuring they are retained until the corresponding antenna's turn comes up again. Additionally, there is another demultiplexer that generates enable signals for these latches, ensuring proper synchronization of the threshold values, see Figure 2.5.

Figure 2.5 Block Diagram of MAD/MoM Multiplexed Architecture

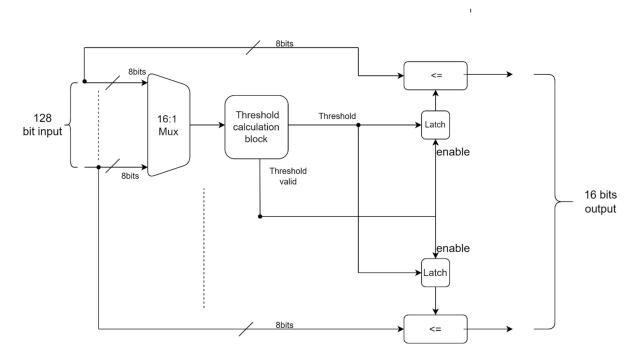

We have also implemented an alternative method called the Single MAD/MoM Design, depicted in Figure 2.6, where we eliminate the need for rotating the threshold and instead calculate it directly based on a single antenna input.

Figure 2.6 Single MAD / MOM Multiple Detection

#### 2.5 Need for Optimization

During the design process of the proposed architecture, careful consideration is given to the utilization of resources not only within the architecture itself but also in the larger context of the TPM hardware and overall design. It is crucial to optimize resource utilization to ensure efficient operation and seamless integration of the architecture into the larger design framework. This approach ensures that the proposed architecture aligns effectively with the TPM hardware and contributes to the overall success of the project.

| Resources | ТРМ  | MAD without filter | Multiplexed MAD scheme<br>(V1) |

|-----------|------|--------------------|--------------------------------|

|           | (%)  | (%)                | (%)                            |

| LUTS      | 59.9 | 2.28               | 2.9                            |

| SLICES    | 88.4 | 10.2               | 11                             |

| BRAM      | 42.2 | 0.9                | 0.44                           |

| DSPs      | 66.7 | 0                  | 0.08                           |

Table 2.1 Resource Utilization Table (16k window)

The utilization of SLICES in the FPGA has reached a significant level of 99.4%. This indicates that the current resource utilization is approaching the maximum threshold and careful consideration should be given to resource management and optimization to ensure the proper functioning of the FPGA.

In this project, two optimized versions have been proposed to address the high resource utilization issue. These versions involve reducing the utilization of SLICES by leveraging the utilization of DSP slices. By strategically utilizing DSP slices, we aim to optimize resource allocation and achieve a more efficient design that minimizes overall resource utilization while maintaining the desired functionality.

# Chapter 03: Analysis of TPM Data

#### 3.1 Data Format

We received the TPM data for 5 days from March 2022. The received data is from the TPM site with 50-350 MHz RF and sampled at 1.25 ns (800 MHz) sampling period. The files were in zipped format. Following are the details of the files.

Format of the file name: YYYY-MM-DD Terra15 Tile-16.tar

After extracting this file a folder with the same name is created, each folder varies in size from 6.5 Gbs to 8.5 GB approximately, depending on the number of files it contains.

Each folder contains around 2.8K to 5.5K files, all these files are in .hdf5 format, and are further extracted using a Python script, which converts them into .out format.

Format of the file name: raw\_burst\_15\_YYYYMMDD\_XXXX\_0.hdf5

Among the four Python scripts provided with the data, one particular script holds significant importance. This script generates a crucial output file that encompasses data for 16 antenna dual poles. The resulting file comprises 32 columns, each representing data for 100 or more bursts. It is noteworthy that each burst consists of 32768 voltage samples. Leveraging this vital file, we have developed a Python tool specifically designed for the analysis of TPM data.

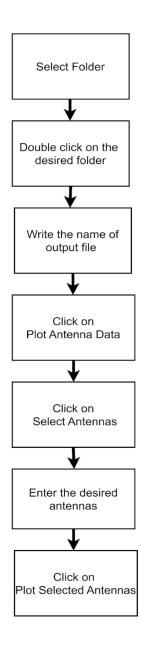

## 3.2 Python Tool

We have developed a Python tool for analyzing long TPM data that allows manual analysis and identification of significant bursts of RFI. The tool is designed as a graphical user interface (GUI) using Tkinter, making it user-friendly and intuitive.

Using this tool, one can easily extract data from HDF5 files and generate output files in the .out format. The user has the flexibility to choose the desired name for the output file. The output file contains 32 columns, representing the data of 16 antennas with dual polarization. The tool also provides the ability to plot 16 figures simultaneously, allowing for a clear understanding of the data behavior across antennas on the same tile.

One of the key features of the tool is the simplified selection of antennas of interest with which the user can conveniently specify their preferences using comma-separated values or a range. The tool validates the selected antennas and generates a plot that showcases the behavior of the chosen antennas on a single tile. The 16 subplots in the figure enable users to visualize and analyze the antenna data effectively.

By streamlining the process of data extraction and visualization, the tool enhances the manual analysis of TPM data. Users can identify significant RFI bursts and gain insights into the behavior of different antennas. The tool is quite useful in quick time domain analysis of the TPM Data.

The flow is shown in section 3.3.

## 3.3 Flowchart of Tool

A brief flow of the tool is shown in Figure 3.1, the user has to follow these steps to extract and plot the TPM data.

Figure 3.1 Flowchart of Tool

#### 3.4 Time Domain Analysis

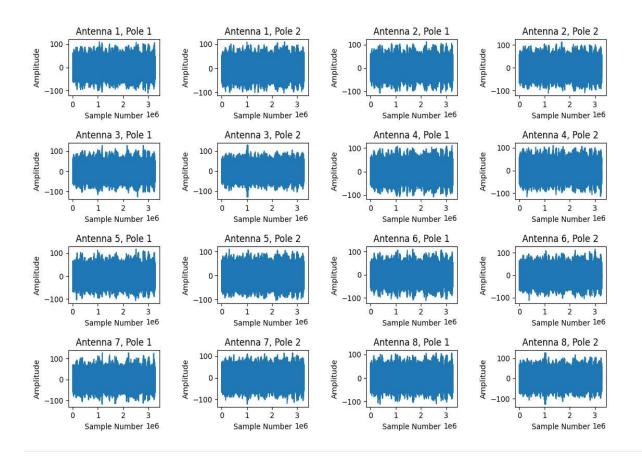

Time domain analysis is done on TPM data to find the similarity of the data between the antennas on the same tile. The data plotted here is from 03/03/2022.

Here is a sample plot:

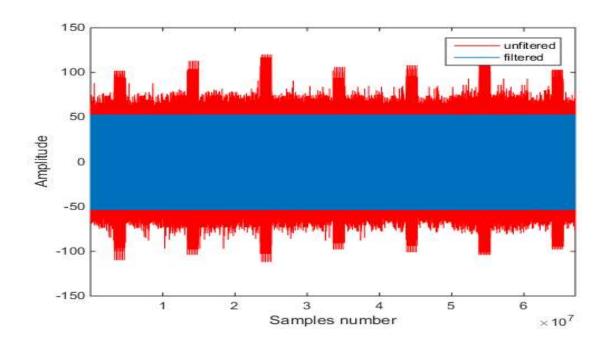

Figure 3.2 Time domain analysis

As it is clear from Figure 3.2 that the data pattern is the same for the antennas on the same tile. So we can also propose a single threshold scheme for all the antennas on one tile. As the separation between them is quite less.

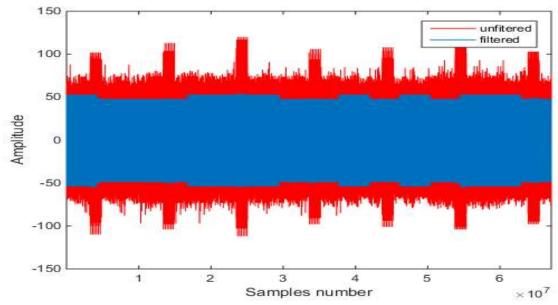

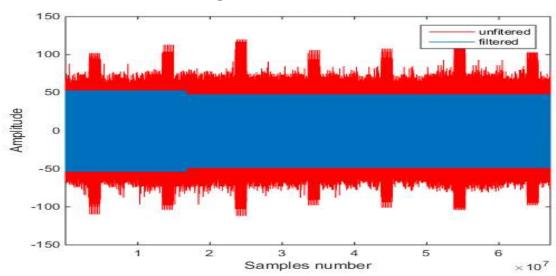

Analyzing the data with MATLAB to determine an appropriate window size for the detection based on the methods of MoM and MAD.

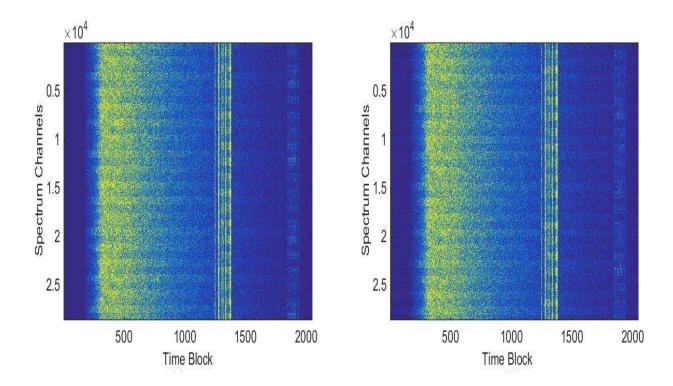

Figure 3.3 MoM with 2k window size

Figure 3.4 MoM with 4k window size

Figure 3.5 MoM with 8k window size

As it is quite evident from the Figures 3.3, 3.4, 3.5, 4k and 8k are the best window sizes for MOM filtering, 4k and 8k are quite effective in filtering the data. But considering the constraints for resources we concluded that 4k is best for our use.

## 3.5 Frequency Domain Analysis

Frequency domain analysis is a valuable technique that involves analyzing signals by decomposing them into their constituent frequency components. It allows for the identification of specific frequencies or frequency ranges of interest and provides insights into signal characteristics.

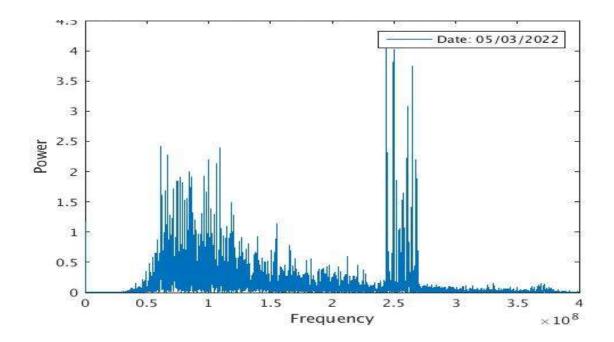

Figure 3.6 Cross-Correlation Spectrum

Auto-correlation and Cross-correlation are two important statistical methods used in Frequency domain analysis. On one hand, auto-correlation helps us find whether a signal distorted by noise is periodic or not, on the other hand, cross-correlation helps us find the copy of one signal into another noisy signal.

We did the cross-correlation of the filtered and unfiltered data, and as we can clearly see from the graph the output is highly correlated, which suggests that the signal information is not lost during filtering of data. The spike that we see in Figure 3.5 is RFI.

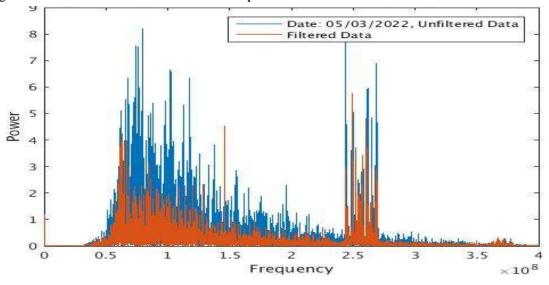

In Figure 3.6, we presented a power spectrum plot(auto-correlation) comparing the filtered and unfiltered data. The graph clearly illustrates that the filtered data exhibits fewer/lower RFI compared to the unfiltered data. This observation signifies the effectiveness of the MOM (Median of MAD) filtering technique in successfully removing RFI. The reduction in power

spikes indicates that the filtering process significantly mitigates the impact of RFI on the signal, leading to a cleaner and more reliable data representation.

Figure 3.7 Power Spectrum Overlay for Unfiltered and Filtered Data

Figure 3.8 Average Power Spectrum for unfiltered and filtered data

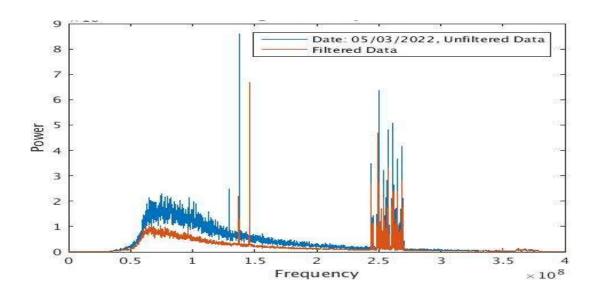

To remove the high-frequency noise we did the power averaging in Figure 3.7 which acts as a low pass Filter. We plotted Average Power Spectrum for better visualization in Figure 3.8.

Figure 3.9 Average Power Spectrum

## **Chapter 04: Optimization**

As mentioned in Chapter 02, due to limited resources in the TPM module, an optimized approach was necessary. In this regard, we found that the DSP slices were underutilized, leaving room for more efficient utilization to reduce the over-utilization of CLB slices.

To achieve this, we strategically relocated the accumulators of our design to the inbuilt DSP accumulators, thereby making better use of the available resources and improving overall efficiency.

## 4.1 Optimized MAD Multiplexed Design

| Resources | TPM (%) | MAD without filter | Multiplexed MAD scheme (V1) (%) | Multiplexed MAD scheme (Accum in dsp)(V2) |

|-----------|---------|--------------------|---------------------------------|-------------------------------------------|

| LUTS      | 59.9    | 2.28               | 2.9                             | 2.9                                       |

| SLICES    | 88.4    | 10.2               | 11                              | 10.79                                     |

| BRAM      | 42.2    | 0.9                | 0.44                            | 0.44                                      |

| DSPs      | 66.7    | 0                  | 0.08                            | 20.40                                     |

Table 4.1 Resource Utilization MAD Multiplexed

The utilization of DSP slices significantly increased from a mere 0.08% to a substantial 20.40%, indicating a more efficient use of these resources. On the other hand, the utilization of Slices decreased slightly from 11% to 10.79%, further highlighting the successful optimization of the design.

| Signal                    | Description                                                                                                                                        |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| clk                       | Input clock                                                                                                                                        |

| rst                       | Active high, synchronous reset                                                                                                                     |

| hold                      | The control signal for enabling counter output                                                                                                     |

| rst_ram2_counter          | Active high, Synchronous reset for address generating counter of Block RAM2 which stores the MAD values                                            |

| rst_comp_median           | Active high, Synchronous reset for comparator block of median                                                                                      |

| rst_counter_median        | Active high, Synchronous reset for a counter block of the median which generates a reset signal for the main accumulator and auxiliary accumulator |

| rst_comp_mad              | Active high, Synchronous reset for comparator block of MAD                                                                                         |

| rst_counter_mad           | Active high, Synchronous reset for a counter block of MAD which generates a reset signal for the main accumulator and auxiliary accumulator        |

| rst_filter                | Active high, Synchronous reset for filter block                                                                                                    |

| rst_count                 | Active high synchronous reset for counter that controls mux and demux                                                                              |

| count                     | The control signal for the counter that controls mux and demux                                                                                     |

| 8-bit inputs              | Data inputs for 16 antennas.                                                                                                                       |

| rfi_flag_1 to rif_flag_16 | Flag output of the detection block.                                                                                                                |

Table 4.2 VHDL interface of Multiplexed MAD design

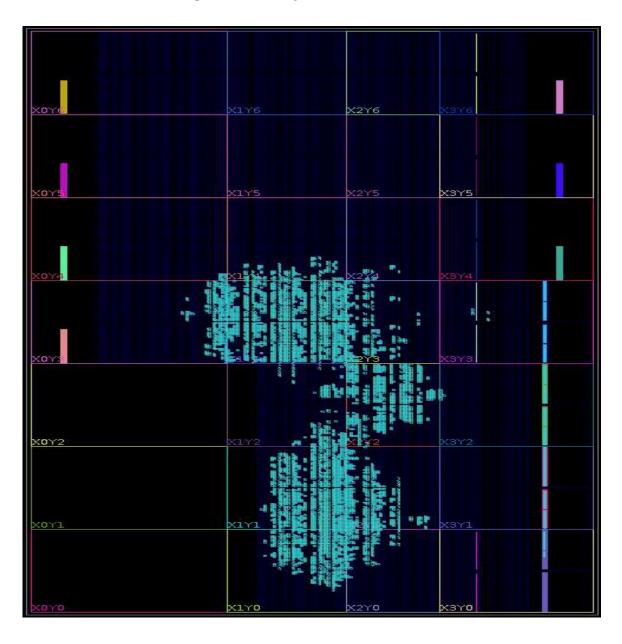

## 4.1.1 Synthesis and Implementation

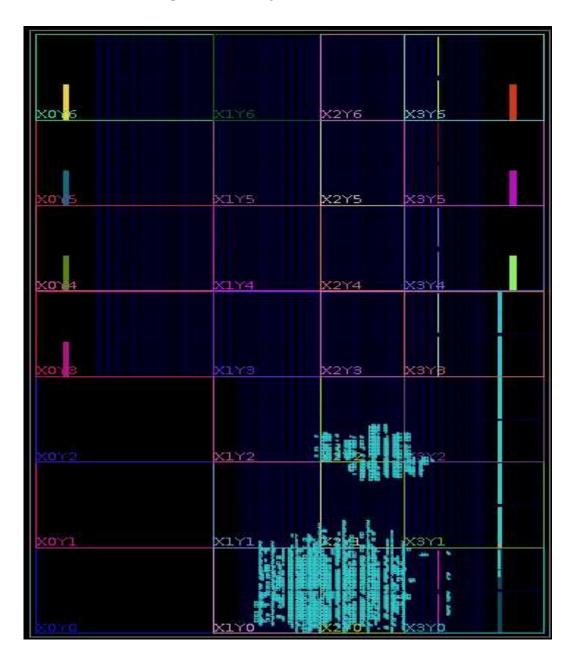

In this section, Synthesis and Implementation details are mentioned. This section contains the FPGA Implementation view of the MAD-Multiplexed design. Moreover, the Timing and Area-Utilizations details of Implemented designs are discussed in this section.

Figure 4.2 Implementation View of MAD Multiplexed Design

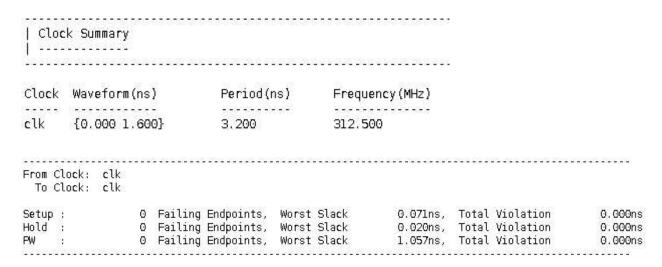

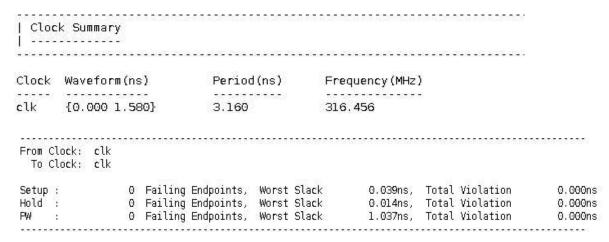

#### 4.1.2 Timing Details

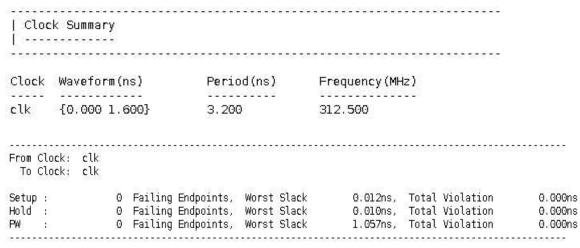

As shown in Figure 4.2, the Filter design works on 312.5 MHz frequency without any STA violation.

Figure 4.2 Timing Report MAD Multiplexed

#### 4.1.3 Utilization details

1. CLB Logic

Figure 4.3 gives an overall idea of resource utilization. There is no register as a latch.

| Site Type             | Used  | Fixed | Available | Util% |

|-----------------------|-------|-------|-----------|-------|

| CLB LUTs              | 7955  | 0     | 274080    | 2.90  |

| LUT as Logic          | 7955  | 0     | 274080    | 2.90  |

| LUT as Memory         | 0     | 0     | 144000    | 0.00  |

| CLB Registers         | 11587 | 0     | 548160    | 2.11  |

| Register as Flip Flop | 11587 | 0     | 548160    | 2.11  |

| Register as Latch     | 0     | 0     | 548160    | 0.00  |

| CARRY8                | 2713  | 0     | 34260     | 7.92  |

| F7 Muxes              | 21    | 0     | 137040    | 0.02  |

| F8 Muxes              | 8     | 0     | 68520     | 0.01  |

| F9 Muxes              | 0     | 0     | 34260     | 0.00  |

Figure 4.3 CLB Utilization MAD Multiplexed

#### 4. ARITHMETIC

| Site Type    | Used | Fixed       | Available | Util%       |

|--------------|------|-------------|-----------|-------------|

| t DSPs       | 514  | ++<br>I 0 I | 2520      | <br>l 20.40 |

| DSP48E2 only |      |             | 2320      |             |

#### 2. CLB Logic Distribution

| Site Type                              | Used  | Fixed | Available | Util%          |

|----------------------------------------|-------|-------|-----------|----------------|

| CLB                                    | 3695  | 0     | 34260     | 10.79          |

| CLBL                                   | 1537  | 0     |           | 1              |

| CLBM                                   | 2158  | i oi  |           | Ĭ.             |

| LUT as Logic                           | 7958  | 0     | 274080    | 2.90           |

| using 05 output only                   | 19    | ĺ     |           | ka paakaaaka   |

| using 06 output only                   | 3341  | ĺ     |           | Ĭ.             |

| using 05 and 06                        | 4598  | į 21  |           | i <sup>e</sup> |

| LUT as Memory                          | 0     | 0     | 144000    | 0.00           |

| LUT as Distributed RAM                 | 0     | 0     |           | l)             |

| LUT as Shift Register                  | 0     | 0     |           | 1              |

| CLB Registers                          | 11572 | 0     | 548160    | 2.11           |

| Register driven from within the CLB    | 9618  |       |           | is:            |

| Register driven from outside the CLB   | 1954  | l il  |           | Ĺ              |

| LUT in front of the register is unused | 1743  | 1 ]   |           | ľ.             |

| LUT in front of the register is used   | 211   |       |           | ľ.             |

| Unique Control Sets                    | 51    | 1 3   | 68520     | 0.07           |

#### 9. Primitives

| Ref Name   | Used         | Functional Category |

|------------|--------------|---------------------|

| FDRE       | +<br>  11587 | Posiston            |

| 1. S. 1977 | 당하고 하고 맛있는 것 | Register            |

| LUT2       | 8369         | CLB                 |

| CARRY8     | 2713         | CLB                 |

| LUT3       | 1638         | [ CLB               |

| LUT6       | 922          | CLB                 |

| LUT5       | 725          | [ CLB               |

| LUT1       | 534          | CLB                 |

| DSP48E2    | 514          | Arithmetic          |

| LUT4       | 368          | CLB                 |

| INBUF      | 147          | 1/0                 |

| IBUFCTRL   | 147          | Others              |

| MUXE7      | 21           | [ CLB               |

| OBUF       | 16           | 1/0                 |

| MUXF8      | 8            | CLB                 |

| RAMB36E2   | 4            | Block Ram           |

| BUFGCE     | ј з          | Clock               |

Figure 4.4 Utilization Report of MAD Multiplexed

# 4.2 Optimized MOM Multiplexed Design

The architecture for MoM multiplexed is the same as MAD multiplexed, but we have made it using the first median 0. The only change is now the threshold is calculated based on MoM.

| Resources | MAD without filter (%) | Multiplexed<br>MAD scheme<br>(V1)<br>(%) | Multiplexed<br>MAD scheme<br>(accum in<br>dsp)(V3) | MAD<br>multiplexed<br>Scheme<br>(first median<br>=0) (V4) | Multiplexed<br>MoM<br>(first<br>median=0)<br>(V5) |

|-----------|------------------------|------------------------------------------|----------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------|

| LUTS      | 2.28                   | 2.9                                      | 2.9                                                | 1.75                                                      | 1.68                                              |

| SLICES    | 10.2                   | 11                                       | 10.79                                              | 6.20                                                      | 6.02                                              |

| BRAM      | 0.9                    | 0.44                                     | 0.44                                               | 0.44                                                      | 0.22                                              |

| DSPs      | 0                      | 0.08                                     | 20.40                                              | 10.24                                                     | 10.24                                             |

Table 4.3 Resource Utilization Multiplexed MoM Design

| Signal                    | Description                                                                                                                                 |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| clk                       | Input clock                                                                                                                                 |

| rst                       | Active high, synchronous reset                                                                                                              |

| hold                      | The control signal for enabling counter output                                                                                              |

| rst_ram2_counter          | Active high, Synchronous reset for address generating counter of Block RAM2 which stores the MAD values                                     |

| rst_comp_mad              | Active high, Synchronous reset for comparator block of MAD                                                                                  |

| rst_counter_mad           | Active high, Synchronous reset for a counter block of MAD which generates a reset signal for the main accumulator and auxiliary accumulator |

| rst_filter                | Active high, Synchronous reset for filter block                                                                                             |

| enable demux              | Active high, Synchronous enable for both demultiplexers.                                                                                    |

| count                     | Control signal for the counter, that controls multiplexer                                                                                   |

| sel_filter(3 downto 0)    | User has given input for selecting the input, which will select the data on which threshold will be calculated                              |

| 8-bit inputs              | Data inputs for 16 antennas.                                                                                                                |

| rfi_flag_1 to rif_flag_16 | Flag output of the detection block.                                                                                                         |

Table 4.4 VHDL interface of MOM multiplexed design

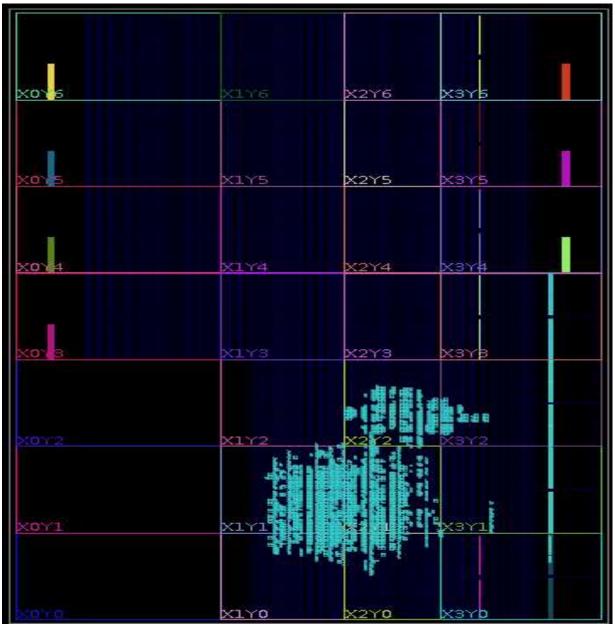

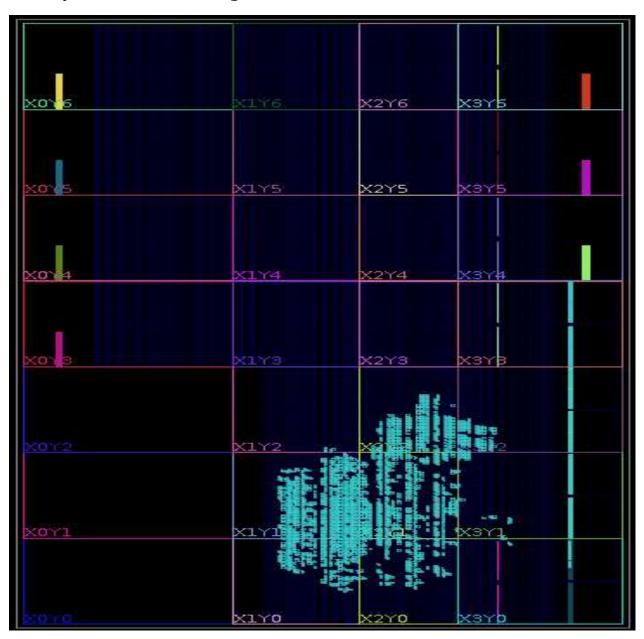

## 4.2.1 Synthesis and Implementation

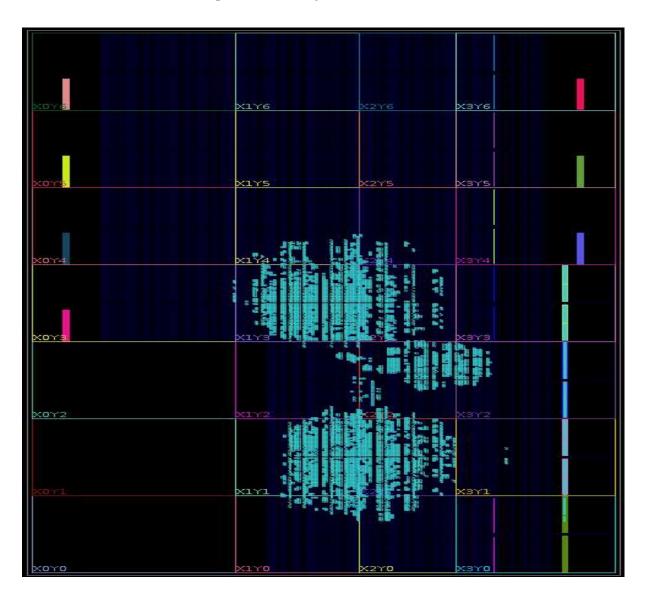

In this section, Synthesis and Implementation details are mentioned. This section contains the FPGA Implementation view of the MoM-Multiplexed design. Moreover, the Timing and Area-Utilizations details of Implemented designs are discussed in this section.

Figure 4.5 Implementation view of MoM Multiplexed Design

## 4.2.2 Timing Details

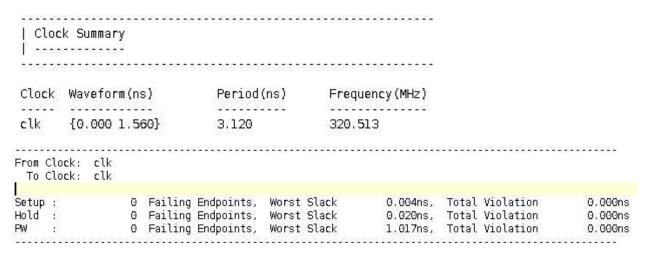

As shown in Figure 4.2, the Filter design works on 312.5 MHz frequency without any STA violation.

Figure 4.6 Timing Report MoM Multiplexed

### 4.2.3 Utilization Details

## 1. CLB Logic

| Site Type             | Used        | Fixed | Available | Util% |

|-----------------------|-------------|-------|-----------|-------|

| CLB LUTs              | +<br>  4580 | l 0 1 | 274080    | 1.67  |

| LUT as Logic          | 4580        | 0     | 274080    | 1.67  |

| LUT as Memory         | 0           | 0     | 144000    | 0.00  |

| CLB Registers         | 6930        | 0     | 548160    | 1.26  |

| Register as Flip Flop | 6930        | 0     | 548160    | 1.26  |

| Register as Latch     | 0           | 0     | 548160    | 0.00  |

| CARRY8                | 1433        | 0     | 34260     | 4.18  |

| F7 Muxes              | 21          | 0     | 137040    | 0.02  |

| F8 Muxes              | 8           | 0     | 68520     | 0.01  |

| F9 Muxes              | 0           | 0     | 34260     | 0.00  |

Figure 4.7 CLB Logic MoM Multiplexed

#### 4. ARITHMETIC

| Site Type   | Used         | Fixed   | Available | Util% |

|-------------|--------------|---------|-----------|-------|

| DSPs        | - +<br>  258 | <br>  0 | 2520      | 10.24 |

| DSP48E2 onl | y   258      | 1       | Ď.        | 1     |

#### 2. CLB Logic Distribution

| Site Type                              | Used | Fixed | Available                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Util% |

|----------------------------------------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| CLB                                    | 2062 | 0     | 34260                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6.02  |

| CLBL                                   | 940  | 0     | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ĺ     |

| CLBM                                   | 1122 | 0     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | i š   |

| LUT as Logic                           | 4580 | 0     | 274080                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1.67  |

| using 05 output only                   | 21   |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| using 06 output only                   | 2042 | i i   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | į į   |

| using 05 and 06                        | 2517 | Î î   | St. No. of the state of the sta | i     |

| LUT as Memory                          | 0    | 0     | 144000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.00  |

| LUT as Distributed RAM                 | 0    | 0     | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ĺ     |

| LUT as Shift Register                  | 0    | 0     | 4 (4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ĺ     |

| CLB Registers                          | 6930 | 0     | 548160                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1.26  |

| Register driven from within the CLB    | 5031 | ĺ     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| Register driven from outside the CLB   | 1899 | Î î   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | i 8   |

| LUT in front of the register is unused | 1651 | i i   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | į į   |